PVT Dynamic Adaptation in PULPv3

From iis-projects

Contents

Short Description

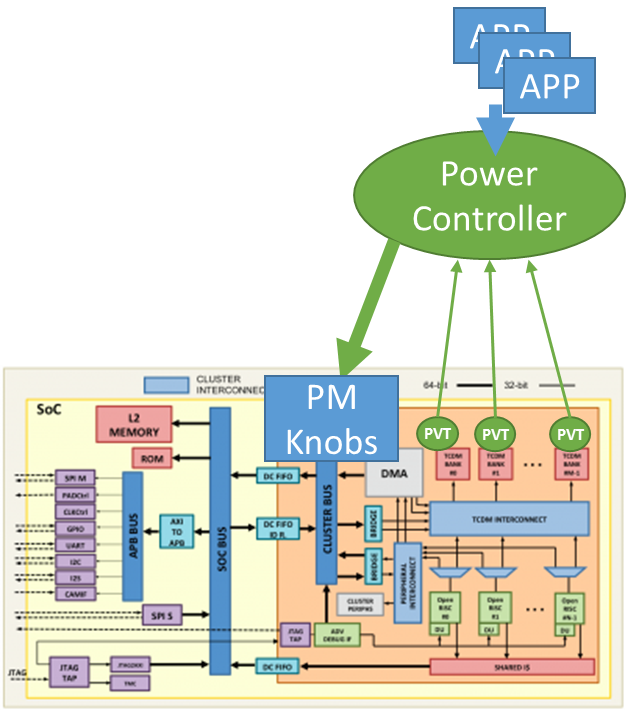

In our research group, Systems on Chip (SoC) with the lowest possible 'energy per operation' are developed ([[1]]). The latest version of PULP features integrated PVT sensors to monitor the silicon state as well as environmental conditions. PVT variation are at the source of large design margin and loss of energy efficiency. In addition PULP features a wide set of power management HW features such fine-grain body-biasing and integrated fine-grain DVFS support. As an effect of the PVT variation the most energy efficiency setting for this parameters shifts changing the silicon speed as well as the leakage to dynamic power ratio. A dynamic power controller algorithm is then needed to always configure the PULP processor in the most energy efficient point.

Goal of this Project The goal of this project is to compensate the process variation in the PULP v3 SoCs by (1) characterize and correlate the PVT sensors response to ambient and process conditions of the chip; (2) implementing the low-level firmware that implements the software control loop which maximizes the energy efficiency of the system dynamically tracking the PVT variations

Status: Available

- Looking for 1 Master Students (Semester Project)

- Supervision: Andrea Bartolini, Antonio Pullini, Davide Rossi

Prerequisites

- VLSI III

- VLSI II

Character

- 20% Theory

- 30% Implementation

- 50% Testing

Professor

Detailed Task Description

Practical Details