File list

From iis-projects

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

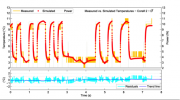

| 20:15, 26 January 2023 | Ifduot.jpg (file) |  |

720 KB | 1 | |

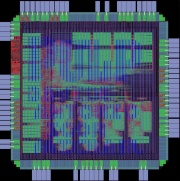

| 20:00, 27 January 2021 | Yourchip.jpg (file) |  |

492 KB | Dustin | 1 |

| 11:38, 22 July 2020 | Pulp slide template v1.1.pptx (file) | 1.43 MB | 1 | ||

| 08:56, 21 October 2019 | Pulp slide template v1.0.pptx (file) | 361 KB | There was a strange information in the properties "Micro Genetic Algorithm (mGA) Group Optimization Methods for Engineers" that made it in to search keywords. Attempt to correct this | 2 | |

| 16:10, 31 January 2019 | NeutronDetector.jpg (file) |  |

100 KB | 1 | |

| 16:36, 21 June 2018 | SolidStatePhysics.png (file) |  |

470 KB | 1 | |

| 21:36, 30 January 2018 | PhysXilinxBoard.png (file) |  |

1.01 MB | 1 | |

| 09:02, 21 December 2017 | Qudev project.jpg (file) |  |

117 KB | 1 | |

| 17:14, 13 November 2017 | Too lazy too busy.jpg (file) |  |

273 KB | I am too lazy to write anything on this page | 1 |

| 08:14, 7 November 2017 | Project map 2017 10.png (file) |  |

182 KB | 1 | |

| 16:17, 24 June 2017 | IBM Phase Change Memory.png (file) |  |

574 KB | 1 | |

| 18:40, 10 May 2017 | Hyperdimensional EMG.png (file) |  |

121 KB | 1 | |

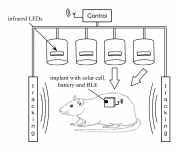

| 16:27, 22 August 2016 | Charger picture with mouse.png (file) |  |

82 KB | 1 | |

| 10:18, 10 March 2016 | Latex template.tar.gz (file) | 1.08 MB | 1 | ||

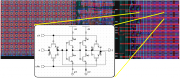

| 15:57, 17 November 2015 | Standard Cell Compatible Memory Array Design.png (file) |  |

942 KB | Concept of the standard cell compatible memory array. | 1 |

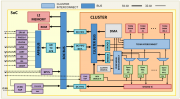

| 18:47, 7 July 2015 | Pulp block diag.png (file) |  |

137 KB | Block diagram of the PULP system | 1 |

| 19:48, 21 May 2015 | Switched capacitor based bandgap.png (file) |  |

480 KB | Taken from Shrivastava, et. al., "A 32nW Bandgap Reference Voltage Operational from 0.5V Supply for Ultra-Low Power Systems", ISSCC 2015 | 1 |

| 15:54, 14 January 2015 | Pulp Efficient Supply.jpg (file) |  |

473 KB | Power management design | 1 |

| 18:19, 8 December 2014 | RiscV.jpg (file) |  |

68 KB | 1 | |

| 17:30, 8 December 2014 | Pll4Pulp.jpg (file) |  |

31 KB | 1 | |

| 20:49, 27 March 2014 | Hardware Accelerator for Model Predictive Controller2.png (file) |  |

103 KB | 1 | |

| 20:48, 27 March 2014 | Hardware Accelerator for Model Predictive Controller1.png (file) |  |

238 KB | 1 | |

| 15:43, 27 March 2014 | Image Sensor Interface and Pre-processing.jpg (file) |  |

71 KB | 1 | |

| 13:32, 27 March 2014 | The default funny picture here.jpg (file) |  |

622 KB | 1 | |

| 17:18, 8 March 2014 | Simulation of the optical properties of nanostructured solar cells.png (file) |  |

105 KB | 1 | |

| 17:14, 8 March 2014 | Simulation of novel solar cell architectures.png (file) |  |

169 KB | 1 | |

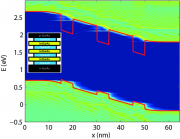

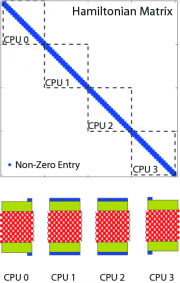

| 17:09, 8 March 2014 | Parallel bandstructure calculation of nanostructures.png (file) |  |

75 KB | 1 | |

| 17:06, 8 March 2014 | GPU-Accelerated Nanoelectronic Device Simulations.jpg (file) |  |

4 KB | 1 | |

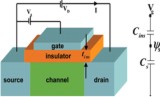

| 16:25, 8 March 2014 | Simulation of Negative Capacitance Ferroelectric Transistor.jpg (file) |  |

12 KB | 1 | |

| 16:21, 8 March 2014 | Computation of Phonon Bandstructure in III-V Nanostructures.png (file) |  |

98 KB | 1 | |

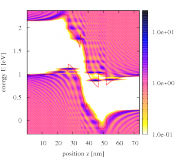

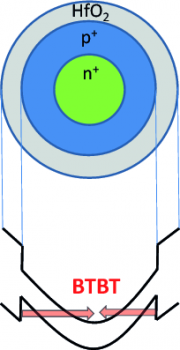

| 15:55, 8 March 2014 | Design study of tunneling transistors.png (file) |  |

48 KB | 1 | |

| 15:52, 8 March 2014 | Creating Full-band simulations Double Heterojunction Bipolar Transistors.jpg (file) |  |

61 KB | 1 | |

| 15:47, 8 March 2014 | Investigation of the source starvation effect.png (file) |  |

45 KB | 1 | |

| 15:36, 8 March 2014 | Open Source Basestation for Evolved EDGE.jpg (file) |  |

22 KB | 1 | |

| 15:26, 8 March 2014 | Android Software Design.jpg (file) |  |

8 KB | 1 | |

| 15:20, 8 March 2014 | Trustworthy Three-Factor Authentication.png (file) |  |

23 KB | 1 | |

| 15:13, 8 March 2014 | Audio DAC Conversion Jitter Measurement.jpg (file) |  |

49 KB | 1 | |

| 15:10, 8 March 2014 | Leveling Loop for Very-Low-Distortion Oscillator.jpg (file) |  |

51 KB | 1 | |

| 15:00, 8 March 2014 | Wiederverwendung.gif (file) |  |

7 KB | 1 | |

| 14:57, 8 March 2014 | Praxisgerechte.gif (file) |  |

7 KB | 1 | |

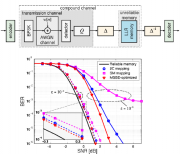

| 10:39, 4 February 2014 | Data Mapping for Unreliable Memories.png (file) |  |

130 KB | Top: Digital communication system employing BPSK transmission over an AWGN channel with unreliable memory. Bottom: Bit-error rate performance of the system assuming convolutional coding for different data representations. | 1 |

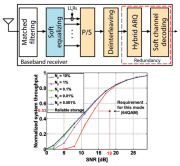

| 10:33, 4 February 2014 | Exploitation of Inherent Error Resilience of Wireless Systems.png (file) |  |

187 KB | Top: Simplified block diagram of the considered 3GPP TD-HSPA wireless communication system (receive side). Bottom: Throughput performance of the system including re-transmissions with hybrid-ARQ for various defect rates. | 1 |

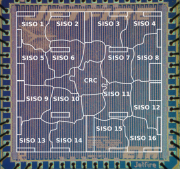

| 10:24, 4 February 2014 | High Throughput Turbo Decoder Design.png (file) |  |

804 KB | Chip micrograph of the LTE-Advanced turbo decoder. The overlay depicts the exact locations of the 16 parallel SISO decoders used to achieve the 1Gbps throughput. | 1 |

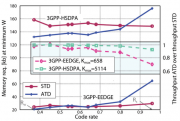

| 10:18, 4 February 2014 | Turbo Decoder Design for High Code Rates.png (file) |  |

181 KB | The impact of code rate on throughput and memory capacity of traditional acquisition-run-based turbo decoders (ATD) and state-metric-propagation-based turbo decoder implementations (STD). | 1 |

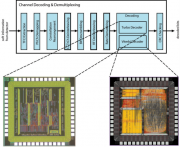

| 10:10, 4 February 2014 | Channel Decoding for TD-HSPA.png (file) |  |

300 KB | Top: High-level architecture of the channel decoding chain for the downlink terminal side of 3GPP TD-HSPA. Bottom: Layout of the fabricated turbo and Viterbi decoder prototypes integrated in 180 nm CMOS technology. | 1 |

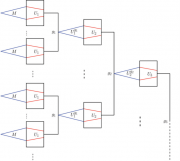

| 18:01, 30 January 2014 | Progressive grouping stage with MLD pruning.png (file) |  |

72 KB | A tree portion of the progressive grouping stage with MLD pruning, which is used in the pre-processing step in a low-complexity sequence detector. | 1 |

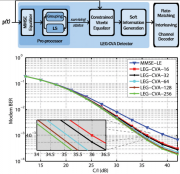

| 17:47, 30 January 2014 | Block diagram of the LEG-CVA receiver.png (file) |  |

355 KB | Top: A block diagram of the LEG-CVA receiver. Bottom: Modem Bit-Error-Rate vs. Received Signal-to-Noise Power Ratio for TD-HSPA, Case-3 Multipath Channel, 16-CDMA codes and 64-QAM. | 1 |

| 17:27, 30 January 2014 | Successive interference cancellation multi user detector.png (file) |  |

192 KB | Performance of the successive interference cancellation multi user detector (SIC-MUD) and the corresponding hardware implementation compared to the traditional linear MMSE equalizer. | 1 |

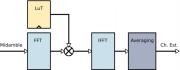

| 17:21, 30 January 2014 | Basic working principle of the Steiner channel estimator.png (file) |  |

25 KB | Basic working principle of the Steiner channel estimator | 1 |

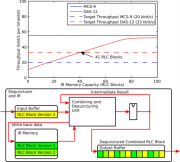

| 17:11, 30 January 2014 | High-level dedicated IR architecture storing punctured RLC blocks.png (file) |  |

135 KB | Top: Simulation results for coding schemes MCS-9 and DAS-12 in order to evalute IR performance. Bottom: High-level dedicated IR architecture storing punctured RLC blocks. | 1 |

First page |

Previous page |

Next page |

Last page |