VLSI Implementation Polar Decoder using High Level Synthesis

From iis-projects

Short Description

Recently the 3GPP standardization group decided to adopt Polar codes as a new forward error correction scheme for the upcoming 5th-generation cellular communication standards (5G). Polar codes were introduced by Arikan only in 2009. The underlying idea is to separate the different virtual channels observed by each transmitted bit into good and bad channels. When sending information only over these good virtual channels it can be proven that Polar codes achieve the Shannon capacity for binary, discrete, memoryless channels. This is why Polar codes have been one of the main focus of research in the communication’s society. The recent decision by the 3GPP standardization group now puts Polar codes into real application scenarios for the first time.

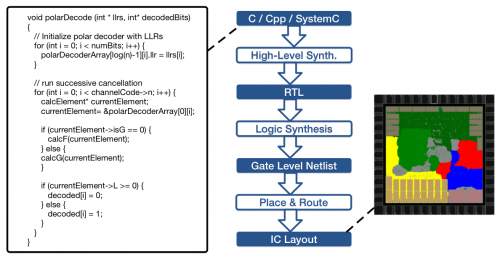

The goal of this project is the development of an efficient Polar decoder VLSI macro targeting 5G cellular application. Thereby, the decoder macro shall be modeled in a high-level description language like Cpp followed by an automated RTL generation using high-level synthesis. Such a high-level synthesis design flow does not only reduce the design time itself, it also allows for an architectural design space exploration in which various decoder architectures can be quantitatively evaluated based on the generated RTL. In order to improve the quality of results, manually optimized RTL code or even full-custom-designed hard macros of critical components can be introduced into the high-level synthesis flow.

Status: Available

- Looking for 1 Master student

- Contact: Matthias Korb

Prerequisites

- Knowledge in C/Cpp and VHDL

Character

- 20% Theory, Algorithms, and Simulation

- 50% Modeling of Polar decoder in synthesizable Cpp/SystemC

- 30% Full-custom design of critical components