Compressed Sensing Reconstruction on FPGA

From iis-projects

Short Description

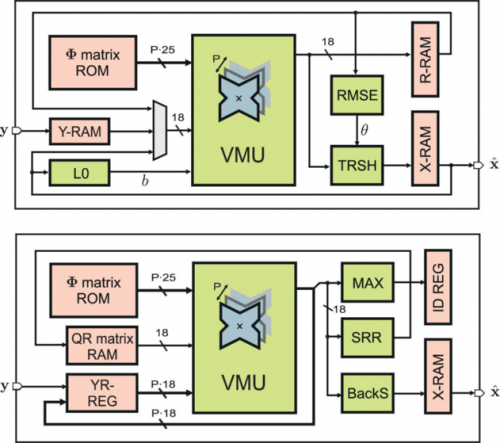

Compressed sensing allows to reconstruct sparse signals sampled at sub-Nyquist rates. However, reconstruction of the original signal requires high computational effort, even for problems of moderate size. Especially for applications with real-time requirements, software realizations are not fast enough. We therefore implemented generic high- speed FPGA implementations of two fast reconstruction algorithms: orthogonal matching pursuit (OMP) and ap- proximate message passing (AMP). Our implementations also support less sparse signals than previous designs, which makes them suitable for, e.g., image reconstruction.

The FPGA implementations are based on massively parallel computation and make use of the many multipliers available on today’s large FPGAs. Up to 256 parallel multipliers concurrently perform matrix vector multiplica- tions in our design. Both algorithms were found to benefit strongly from parallel processing. Challenges in the design were parallel memory access to provide input for all multipliers at high data-rates and pipelining of interconnections with large word widths.

The RTL implementations of the two similar algorithms allowed for comparisons in terms of resource usage and performance. We could show which algorithm performs better at which sparsity level. While both FPGA imple- mentations provide a significant speed-up compared to software realizations, one algorithm was shown to better fit a hardware structure than the other. A USB interface to a PC allowed to demonstrate the reconstruction capabili- ties using sub-sampled images.

Status: Completed

- Fall Semester 2011 (msc11h16)

- Lin Bai

- Supervisors: Patrick Maechler, Michael Muehlberghuber

Professor

Publications

- L. Bai, P. Maechler, M. Muehlberghuber, H. Kaeslin, "High-Speed Compressed Sensing Reconstruction on FPGA Using OMP and AMP",

IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Seville, Spain, 9-12 Dec 2012