Difference between revisions of "Design of State Retentive Flip-Flops"

From iis-projects

(Created page with "==Short Description== 200px|thumb|left|State Retentive Flip-Flop Power gating is a well-established method to save power in circuit parts currently not in u...") |

(→Short Description) |

||

| Line 4: | Line 4: | ||

Power gating is a well-established method to save power in circuit parts currently not in use in a system on chip (SoC). In contrast to clock gating, where the clock signal is disabled to silence any activity and hence reduce dynamic power consumption, power gating also reduces static dissipation including leakage by completely cutting the power to unused circuit parts. | Power gating is a well-established method to save power in circuit parts currently not in use in a system on chip (SoC). In contrast to clock gating, where the clock signal is disabled to silence any activity and hence reduce dynamic power consumption, power gating also reduces static dissipation including leakage by completely cutting the power to unused circuit parts. | ||

| − | One main drawback of power gating is that the power gated circuit loses its state. While this is acceptable for some sub-circuits, like a small hardware accelerator with no relevant information to be retained between two calls, it is not acceptable for an entire processor core idling, while waiting for a DMA transfer to be | + | One main drawback of power gating is that the power gated circuit loses its state. While this is acceptable for some sub-circuits, like a small hardware accelerator with no relevant information to be retained between two calls, it is not acceptable for an entire processor core idling, for example while waiting for a DMA transfer to be completed. |

In such a scenario, '''State Retentive Power Gating (SRPG)''' is required. On way to implement SRPG is to replace all registers in the power gated domain by special state retentive flip-flops. These special registers are supplied by two voltages: the primary supply, which is turned off during power gating and an auxiliary supply, which is left powered in order to retain the state. | In such a scenario, '''State Retentive Power Gating (SRPG)''' is required. On way to implement SRPG is to replace all registers in the power gated domain by special state retentive flip-flops. These special registers are supplied by two voltages: the primary supply, which is turned off during power gating and an auxiliary supply, which is left powered in order to retain the state. | ||

| − | The goal of this thesis is to build a state retentive flip-flop standard cell and integrate it in our tool-flow. | + | The goal of this thesis is to build a state retentive flip-flop standard cell and integrate it in our tool-flow. This requires transistor-level design of the circuit, characterization of this cell for timing and power, updating the necessary views (i.e. LIB, LEF) so that it can be integrated in the standard design flow. In a second step, the student will implement state retentive power gating in an existing design using his newly designed cell. Finally, the design will be taped out to validate and characterize the designed cell. |

| − | In a second step, the student will implement state retentive power gating in an existing design using his newly designed cell. | ||

| − | Finally, the design will be taped out to validate and characterize the designed cell. | ||

The scope of the project will be reduced in the case of a Semester Thesis. | The scope of the project will be reduced in the case of a Semester Thesis. | ||

Revision as of 13:47, 13 November 2015

Contents

Short Description

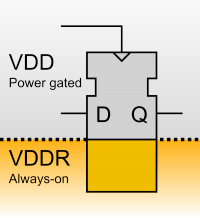

Power gating is a well-established method to save power in circuit parts currently not in use in a system on chip (SoC). In contrast to clock gating, where the clock signal is disabled to silence any activity and hence reduce dynamic power consumption, power gating also reduces static dissipation including leakage by completely cutting the power to unused circuit parts.

One main drawback of power gating is that the power gated circuit loses its state. While this is acceptable for some sub-circuits, like a small hardware accelerator with no relevant information to be retained between two calls, it is not acceptable for an entire processor core idling, for example while waiting for a DMA transfer to be completed.

In such a scenario, State Retentive Power Gating (SRPG) is required. On way to implement SRPG is to replace all registers in the power gated domain by special state retentive flip-flops. These special registers are supplied by two voltages: the primary supply, which is turned off during power gating and an auxiliary supply, which is left powered in order to retain the state.

The goal of this thesis is to build a state retentive flip-flop standard cell and integrate it in our tool-flow. This requires transistor-level design of the circuit, characterization of this cell for timing and power, updating the necessary views (i.e. LIB, LEF) so that it can be integrated in the standard design flow. In a second step, the student will implement state retentive power gating in an existing design using his newly designed cell. Finally, the design will be taped out to validate and characterize the designed cell.

The scope of the project will be reduced in the case of a Semester Thesis.

Status: Available

- Semester/Master Thesis

- Supervision: Pascal Alexander Hager, Frank K. Gurkaynak

Professor

Character

- 40% Standard cell design

- 30% Toolflow Integration

- 30% Implement state retentive power gating in existing design

Requirements

VLSI 2, AIC is a plus