Design study of tunneling transistors based on a core/shell nanowire structures

From iis-projects

Contents

Short Description

Band-to-band tunneling transistors (TFETs) represent a new kind of logic switches that bear a huge potential as active components of next-generation, energy-efficient, integrated circuits. Contrary to standard metal-oxide-semiconductor field-effect transistors (MOSFETs), the sub-threshold slope (SS) of TFETs is not limited to 60 mV/dec at room temperature, but could theoretically be reduced to very low values. TFETs currently face two major challenges:

- it is rather difficult to fabricate devices with SS below 60 mV/dec and

- their ON-current is usually limited to 10 A/m or less.

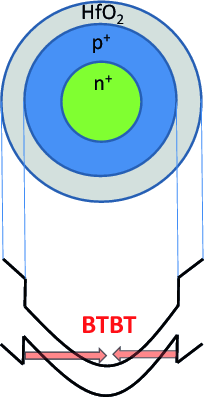

The goal of this project is therefore to investigate the characteristics of a new TFET architecture that could provide better performance than standard ones. The key idea consists in using a core/shell nanowire structure where the core and the shell have different doping types and are eventually made of different materials (see adjacent figure). As simulation engine, the commercial TCAD tool S-Device from Synopsys will be used first to analyze the behavior of such TFETs. If possible, verifications with a more advanced simulator developed at IIS should be performed.

Status: Available

- Looking for 1 Semester/Master student

- Contact: Mathieu Luisier

Prerequisites

- Interest in device modeling

Character

- 20% Theory

- 80% Simulations