Physics is looking for PULP

From iis-projects

Contents

Short Description

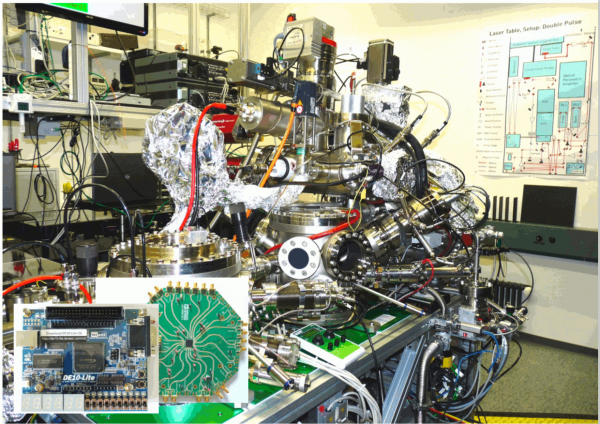

The Solid State Physics Laboratory of ETH Zurich researchers explore innovative research directions with the potential to discover new and potentially useful phenomena in condensed matter. In such environments, you often have to build new and customized measurement and control systems. Optimizing such systems can improve the quality of results, accelerate the rate at which data is sampled and allow new physical phenomena to be observed.

The group is interested in deploying FPGAs in several of their systems. As a start they would like to have a simple FPGA board (Altera DE-10 Lite) where they can have the open source PULP system based on RISC-V processors working. During this project you will map a 32bit PULPino/PULPissimo micro-controller system to the Altera DE-10 Lite board, adapt the design flow so that prospective users can develop their programs, and transfer them to the RISC-V processor, as well as establish connections to basic peripherals. It is planned to make this infrastructure openly available for other educational and research institutions.

Depending on the level (Semester/Master) the project can then be extended to support existing experiments at the laboratory. The project will be co-supervised with D-PHYS.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Frank K. Gürkaynak (IIS), Yves Acremann (D-PHYS)

Prerequisites

- VLSI I (recommended)

Character

- 50% FPGA Design Mapping

- 30% EDA tools

- 20% Applications