Simulation of Negative Capacitance Ferroelectric Transistor

From iis-projects

Contents

Short Description

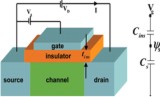

The ongoing scaling of field-effect transistors (FETs) will be soon limited by the difficulty to remove the heat and power dissipated during ON-OFF switching processes. In FETs, the major difficulty to overcome in order to minimize their power consumption is the value of their inverse sub-threshold slope (SS), which determines how much gate voltage is needed to increase the drain current by one order of magnitude. A SS value as low as possible is desired, but due to the thermionic nature of the current flowing through FETs, it is limited to 60 mV/decade at room temperature and cannot go below. Recently, it has been proposed to replace the conventional SiO2 and/or HfO2 dielectric of FETs by a ferroelectric gate stack which could operate as a voltage amplifier induced by the presence of a Negative Capacitance. This could help reduce SS below 60 mV/dec, as recently demonstrated by the group of Prof. Adrian Ionescu at the EPFL. However, fabricating ferroelectric FETs is very complicated and time-consuming. We have therefore recently developed a physics-based simulation tool that can be used to more rapidly investigate the characteristics of such transistors. The goal of this project is now to use this simulator to explore the design space of ferroelectric dielectric layers (thickness, polarization, combination with another insulator layer), determine under which conditions a sub-threshold slope below 60 mV/dec can be obtained, and provide design guidelines to the Laboratory of Electronics at the ETHZ.

Status: Available

- Looking for 1 Semester/Master student

- Contact: Mathieu Luisier, Dr. Giovanni A. Salvatore, ETZ H90, Tel: 22 377, e-mail

Prerequisites

- Knowledge of transistor physics and simulation methods

Character

- 30% Literature Study

- 70% Device Simulations