DMA Streaming Co-processor

From iis-projects

The printable version is no longer supported and may have rendering errors. Please update your browser bookmarks and please use the default browser print function instead.

Short Description

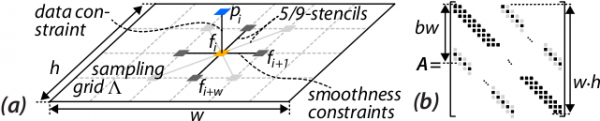

Linear solvers can be used in many image and video processing applications, e.g. for optical-flow calculation or image domain warping (IDW). In a recent publication we estimated the area, throughput and power consumption for different solver implementations, and we would now like to verify some of these estimated results using post-layout simulations and ASIC measurements. Besides the verification of these results, we are interested in how well estimation methods at various levels (pre-RTL estimations, gate-level simulations, post-layout simulations) actually match with the measurements of a fabricated ASIC.

Status: Available

- Scope: Semester or Master Thesis

- Looking for 1-2 Interested Students

- Supervisors: Frank Gürkaynak, Michael Schaffner

Prerequisites

- VLSI I

- Basic Linear Algebra Course

- Matlab, VHDL and C++

Character

- 25% Theory & Literature Study

- 25% Evaluations

- 50% Hw Architecture & ASIC Implementation