Difference between revisions of "3D Turbo Decoder ASIC Realization"

From iis-projects

m (Belfanti moved page 3D Turbo Coder ASIC Realization to 3D Turbo Decoder ASIC Realization) |

|||

| Line 51: | Line 51: | ||

[[#top|↑ top]] | [[#top|↑ top]] | ||

| + | [[Category:Hot]] | ||

[[Category:Digital]] | [[Category:Digital]] | ||

[[Category:Available]] | [[Category:Available]] | ||

Revision as of 11:27, 16 April 2014

Contents

Short Description

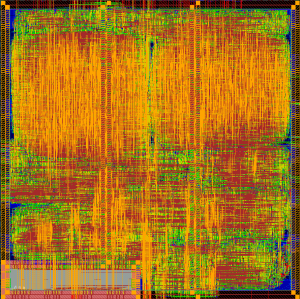

Reliable transmission of information despite unfavorable circumstances is the basis of digital communication. In order to provide good quality of service and high throughput powerful coding schemes are required in almost any application. Turbo codes offer outstanding error correction capabilities combined with efficient hardware architectures, which made them the method of choice in a great variety of applications ranging from 3G/4G cellular networks to satellite communications. Recently a new class of Turbo codes has been proposed, which can improve the error rate even further. Finding an efficient implementation for these 3D-Turbo codes will be your task during this thesis. You will start by evaluating the performance compared to the regular Turbo codes in MATLAB, then design a suitable architecture in order to arrive at a highly efficient VHDL implementation. After the back-end design, the final ASIC will be fabricated in high-end CMOS technology.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Sandro Belfanti

Prerequisites

- VLSI I

- MATLAB and VHDL is an advantage

Character

- 30% Theory/Simulation

- 50% VHDL

- 20% ASIC Implementation