Difference between revisions of "ASIC Development of 5G-NR LDPC Decoder"

From iis-projects

| Line 10: | Line 10: | ||

* Synthesis of the developed RTL code | * Synthesis of the developed RTL code | ||

* Placement and routing of the synthesized design | * Placement and routing of the synthesized design | ||

| + | * A chip tape out is possible if desired by the student | ||

| + | |||

===Status: Available === | ===Status: Available === | ||

| − | : Looking for | + | : Looking for Bachelor/Semester/Master students |

: Contact: [[User:susman | Saleh Usman]] | : Contact: [[User:susman | Saleh Usman]] | ||

| Line 50: | Line 52: | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

| + | [[Category:Bachelor Thesis]] | ||

[[Category:Hot]] | [[Category:Hot]] | ||

[[Category:Available]] | [[Category:Available]] | ||

Revision as of 19:23, 13 November 2020

Contents

Short Description

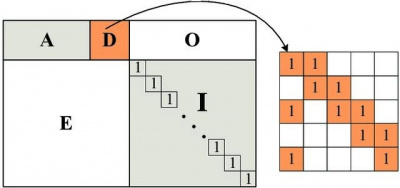

Error-correcting codes enable the correction of transmitted bits received over noisy channels and thus are vital for the contemporary wireless communication systems. Low-Density Parity-Check (LDPC) codes represent a class of high-performance error-correcting codes, and therefore, have been adopted for data transmission in the 5G New-Radio (NR). VLSI implementation of the 5G-NR LDPC decoder is a challenging task because it is defined to support large number of case scenarios for low latency on one hand and high decoding performance on the other side. It is worth working with VLSI implementation of 5G-NR LDPC codes because of their practical relevance and high demand for the 5G wireless communication systems.

Project Description

The goal of this project is to develop an efficient ASIC for a 5G-NR LDPC decoder. We will start by proposing an efficient architecture for the 5G-NR LDOC decoder and then implement it using HDL. The developed HDL code will be synthesized and implemented as an ASIC after placement and routing. The breakdown of the tasks will be as follows:

- Propose architecture for 5G LDPC decoder

- RTL implementation of the proposed architecture

- Synthesis of the developed RTL code

- Placement and routing of the synthesized design

- A chip tape out is possible if desired by the student

Status: Available

- Looking for Bachelor/Semester/Master students

- Contact: Saleh Usman

Prerequisites

- An interest in digital signal processing

- Knowledge in Verilog/VHDL

Character

- 20% Modeling of 5G LDPC decoder in MATLAB/C/Cpp

- 40% Verilog/VHDL implementation

- 40% ASIC design