Difference between revisions of "Accelerator for Boosted Binary Features"

From iis-projects

| Line 44: | Line 44: | ||

* '''[[Final Report]]''' | * '''[[Final Report]]''' | ||

* '''[[Final Presentation]]''' | * '''[[Final Presentation]]''' | ||

| − | |||

| − | |||

---- | ---- | ||

[[#top|↑ top]] | [[#top|↑ top]] | ||

| − | [[Category: | + | [[Category:Image and Video Processing]] [[Category:Digital]] [[Category:Research]] [[Category:Master Thesis]] [[Category:Semester Thesis]] [[Category:Available]] [[Category:FPGA]] |

Revision as of 16:07, 13 May 2015

Contents

Short Description

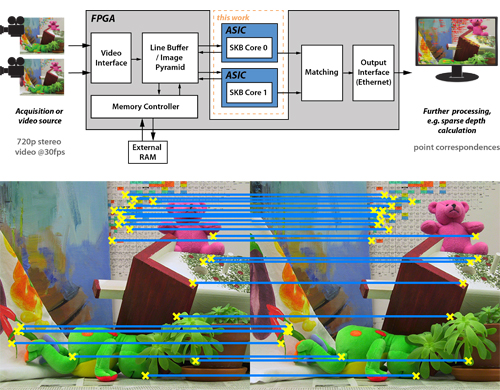

Image feature extraction is an important analysis tool in many computer vision applications. In this context, it is specifically used for sparse depth estimation in stereo video. This project builds upon a previous Semester Thesis (Feature Extraction with Binarized Descriptors: ASIC Implementation and FPGA Environment), where a hardware architecture for image feature extraction has been developed. The goal of this project is to revisit and optimize the existing algorithm and its corresponding architecture. In particular, the focus shall be on controlled approximation of certain sub-steps in the algorithm, since the process of feature extraction and matching is inherently error tolerant.

Status: Available

- Scope: Semester or Master Thesis

- Looking for 1-2 Interested Students

- Supervisors: Frank Gürkaynak, Michael Schaffner

Prerequisites

- VLSI I

- Introductory course in computer vision (recommended)

- Interest in computer graphics / computer vision

- Matlab, VHDL and C++

Character

- 25% Theory & Literature Study

- 35% Matlab Evaluations

- 40% Hw Architecture & FPGA Implementation