Difference between revisions of "Accelerator for Boosted Binary Features"

From iis-projects

m |

|||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 8: | Line 8: | ||

This new descriptor uses a different set of low-level features which have been trained using the AdaBoost learning algorithm, and compared to other | This new descriptor uses a different set of low-level features which have been trained using the AdaBoost learning algorithm, and compared to other | ||

standard algorithms it shows much better performance - at relatively low computational cost. | standard algorithms it shows much better performance - at relatively low computational cost. | ||

| − | ===Status: | + | ===Status: Completed === |

: Scope: Semester or Master Thesis | : Scope: Semester or Master Thesis | ||

: Looking for 1-2 Interested Students | : Looking for 1-2 Interested Students | ||

| − | : Supervisors: [[:User:schaffner|Michael Schaffner]], [[:User: | + | : Supervisors: [[:User:schaffner|Michael Schaffner]], [[:User:Phager | Pascal Hager]] |

===Prerequisites=== | ===Prerequisites=== | ||

| Line 52: | Line 52: | ||

[[#top|↑ top]] | [[#top|↑ top]] | ||

| − | [[Category:Image and Video Processing]] [[Category:Digital]] [[Category:Research]] [[Category:Master Thesis]] [[Category:Semester Thesis]] [[Category: | + | [[Category:Image and Video Processing]] [[Category:Digital]] [[Category:Research]] [[Category:Master Thesis]] [[Category:Semester Thesis]] [[Category:completed]] [[Category:FPGA]] [[Category:2016]] |

Latest revision as of 11:51, 19 August 2017

Contents

Short Description

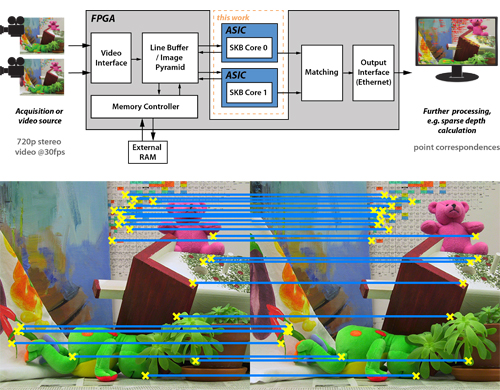

Image feature extraction is an important analysis tool in many computer vision applications. In the context of this project, it is specifically used for sparse depth estimation in stereo video, and sparse flow estimation in normal video. This project builds upon a previous Semester Thesis (Feature Extraction with Binarized Descriptors: ASIC Implementation and FPGA Environment), where a hardware architecture for image feature extraction has been developed. This IP is currently used in the video analysis part of a more complex video processing system which performs automatic multiview conversion in real-time.

The goal of this project is now to extend the existing hardware architecture with a new type of descriptor which has recently been developed at the IIS. This new descriptor uses a different set of low-level features which have been trained using the AdaBoost learning algorithm, and compared to other standard algorithms it shows much better performance - at relatively low computational cost.

Status: Completed

- Scope: Semester or Master Thesis

- Looking for 1-2 Interested Students

- Supervisors: Michael Schaffner, Pascal Hager

Prerequisites

- VLSI I

- Introductory course in computer vision (recommended)

- Interest in computer graphics / computer vision

- Matlab, VHDL and C++

Character

- 25% Theory & Literature Study

- 35% Matlab Evaluations

- 40% Hw Architecture & FPGA Implementation