Difference between revisions of "Channel Estimation for 3GPP TD-SCDMA"

From iis-projects

| Line 38: | Line 38: | ||

<!-- : [http://www.dz.ee.ethz.ch/en/general-information/about/staff/uid/364.html Hubert Kaeslin] ---> | <!-- : [http://www.dz.ee.ethz.ch/en/general-information/about/staff/uid/364.html Hubert Kaeslin] ---> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

[[Category:Digital]] | [[Category:Digital]] | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

[[Category:Available]] | [[Category:Available]] | ||

| + | [[Category:Telecommunications]] | ||

| + | [[Category:Badawi]] | ||

| + | |||

<!-- | <!-- | ||

Revision as of 13:45, 9 February 2015

Short Description

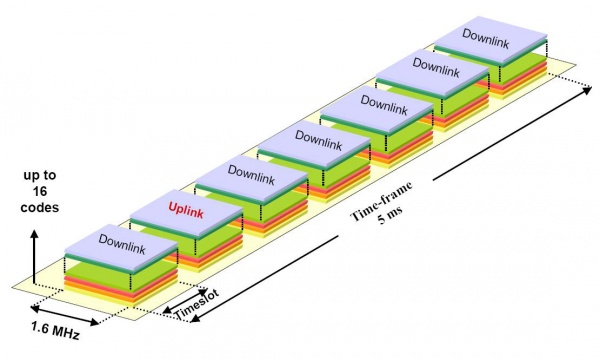

TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptive CDMA component operating in a synchronous mode. Its TDD nature allows to master asymmetric services more efficiently than other 3G standards. Up- and downlink resources are flexibly assigned according to traffic needs, which is helpful in an environment with increasing data traffic, which tends to be asymmetric (mobile Internet).

TD-SCDMA invests a considerable portion of the available bandwidth is pilot symbols, midamples and guard periods. Such information has to be fully and efficiently utilized to obtain -as perfect as possible- channel knowledge. In this thesis, channel estimation techniques shall be investigated focusing on their performance-complexity tradeoff and their impact on successive operations. Therefore, Matlab blocks have to be implemented and integrated within our TD-SCDMA simulation chain, followed by implementation in VHDL code, synthesis and design optimization.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Karim Badawi

Prerequisites

- VLSI I

- Interest in Mobile Communications

- Matlab and VHDL knowledge

Character

- 25% Theory

- 25% Simulation

- 25% Architecture/VHDL

- 25% ASIC Implementation