Difference between revisions of "Covariant Feature Detector on Parallel Ultra Low Power Architecture"

From iis-projects

(Created page with "thumb|600px ==Short Description== Together with the continuous progress on Ultra Low Power (ULP) accelerators we are developing the first Computer Vi...") |

|||

| Line 6: | Line 6: | ||

In this project, you will port a set of existing vision algorithms, based on the VlFeat library [1], on the PULP platform, dealing with parallel programming challenging, low-power computational constraints as well as limited hardware features (e.g. the absence of a Floating Point Unit). | In this project, you will port a set of existing vision algorithms, based on the VlFeat library [1], on the PULP platform, dealing with parallel programming challenging, low-power computational constraints as well as limited hardware features (e.g. the absence of a Floating Point Unit). | ||

The algorithms to be ported on the target architecture refers to the Covariant Feature Detector family, where the purpose of a covariant detector is to extract from an image a set of local features in a manner which is consistent with spatial transformations of the image itself. More in detail the proposed algorithms are: | The algorithms to be ported on the target architecture refers to the Covariant Feature Detector family, where the purpose of a covariant detector is to extract from an image a set of local features in a manner which is consistent with spatial transformations of the image itself. More in detail the proposed algorithms are: | ||

| − | + | * Harris corner [2] | |

| − | + | * Hessian blobs [3] | |

| − | + | * Laplacian and Difference of Gaussian (LoG, DoG) [4] | |

The goal of the project is not only to achieve good performance in term of execution time, but also to find the best trade-off between feature's accuracy and computation time for this platform. In particular the goals of the project can be summarized as follows: | The goal of the project is not only to achieve good performance in term of execution time, but also to find the best trade-off between feature's accuracy and computation time for this platform. In particular the goals of the project can be summarized as follows: | ||

| − | + | * Acquiring familiarity with development on the PULP architecture (available as virtual platform and FPGA) | |

| − | + | * Achieving a good knowledge of the proposed algorithms | |

| − | + | * Porting/development and optimization of Covariant Feature Detectors proposed | |

| − | + | * Measurement of performance and accuracy of the proposed solution | |

===Status: Available === | ===Status: Available === | ||

| Line 27: | Line 27: | ||

===Prerequisites=== | ===Prerequisites=== | ||

| − | : Familiarity with embedded C programming | + | : Familiarity with embedded C programming. |

| − | : Knowledge of parallel computing would be an asset | + | : Knowledge of parallel computing would be an asset. |

: Basic understanding of fundamental CV concepts is favorable. | : Basic understanding of fundamental CV concepts is favorable. | ||

| Line 53: | Line 53: | ||

[[Category:Dpalossi]] | [[Category:Dpalossi]] | ||

[[Category:Marongiu]] | [[Category:Marongiu]] | ||

| − | [[Category:Computer | + | [[Category:Computer Vision]] |

<!-- | <!-- | ||

Revision as of 19:09, 11 January 2016

Contents

Short Description

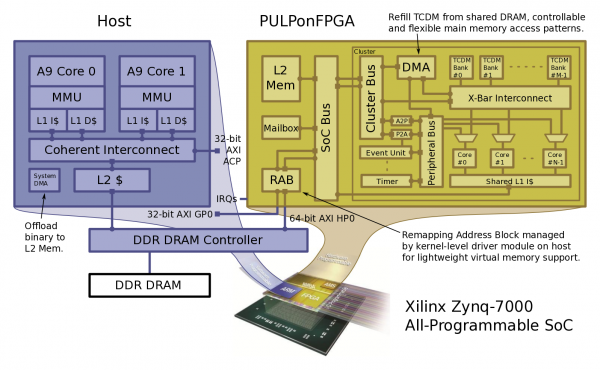

Together with the continuous progress on Ultra Low Power (ULP) accelerators we are developing the first Computer Vision (CV) library in such domain. The development of a CV library featuring high level capabilities is key tackling real word problems such as wearable devices, smart IoT (Internet of Things) sensors and intelligent nano-vehicles. The proposed project take place in this very context and it is meant to operate on the Parallel ULP (PULP) architecture we developed here at the IIS: a scalable, clustered many-core computing platform designed to operate on a large range of operating voltages, achieving in this way a high level of energy efficiency over a wide range of application workloads. In this project, you will port a set of existing vision algorithms, based on the VlFeat library [1], on the PULP platform, dealing with parallel programming challenging, low-power computational constraints as well as limited hardware features (e.g. the absence of a Floating Point Unit). The algorithms to be ported on the target architecture refers to the Covariant Feature Detector family, where the purpose of a covariant detector is to extract from an image a set of local features in a manner which is consistent with spatial transformations of the image itself. More in detail the proposed algorithms are:

- Harris corner [2]

- Hessian blobs [3]

- Laplacian and Difference of Gaussian (LoG, DoG) [4]

The goal of the project is not only to achieve good performance in term of execution time, but also to find the best trade-off between feature's accuracy and computation time for this platform. In particular the goals of the project can be summarized as follows:

- Acquiring familiarity with development on the PULP architecture (available as virtual platform and FPGA)

- Achieving a good knowledge of the proposed algorithms

- Porting/development and optimization of Covariant Feature Detectors proposed

- Measurement of performance and accuracy of the proposed solution

Status: Available

- Looking for Interested Semester and Master Project Students

- Supervision: Daniele Palossi, Andrea Marongiu

Character

- 20-30% Theory

- 30-40% Implementation

- 30-40% Optimization

- 20-30% Testing & Evaluation

Prerequisites

- Familiarity with embedded C programming.

- Knowledge of parallel computing would be an asset.

- Basic understanding of fundamental CV concepts is favorable.