Design-Space Exploration of Low-Resolution Matrix-Vector Multipliers

From iis-projects

Contents

Short Description

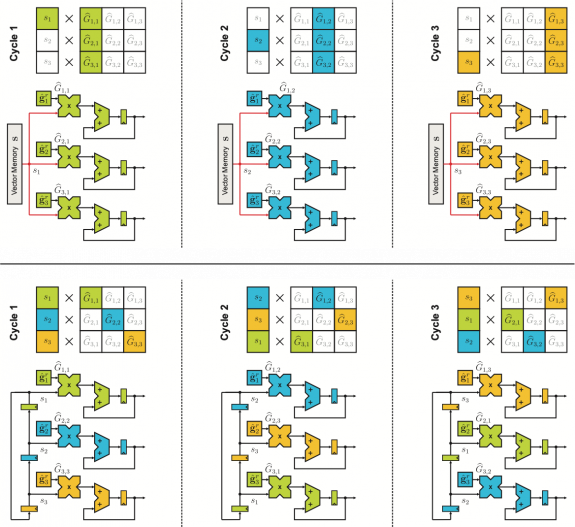

Matrix-vector products are a fundamental operation in many signal processing applications, and they have come to take center stage with the rise of machine learning and 5G wireless systems. While in the end a matrix-vector product is nothing but a collection of multiplications and additions, these operations can be executed in different ways, for example, by (i) performing several inner products, (ii) accumulating outer products, or (iii) by applying Cannon’s algorithm. Despite their importance, there exist no systematic studies that have compared in-depth the different methods to compute a matrix-vector product.

In this project, the goal is to implement generators for different matrix-vector-product engines, so that then we can implement such engines for different parameters (matrix dimensions and number of bits of resolution), and determine when each approach is more convenient than the rest. We will be focusing on matrices and vectors with low-resolution entries, so we will also consider bit-serial, massively-parallel architectures within our study. We will be specially interested in applications for which the matrix is relatively constant, so we will explore processing-in-memory approaches as well. Part of the objective is not only to identify the regimes in which each matrix-vector-product architecture is more advantageous (in terms of throughput or energy-efficiency) than the rest, but also to provide an open-source HDL generator to easily create such architectures. This project requires knowledge of digital logic and VLSI implementation.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Oscar Castañeda

Prerequisites

- VLSI I

- VLSI II (recommended)

Character

- 50% VLSI Design

- 30% Scripting

- 20% Exploration