Difference between revisions of "Design and Implementation of an Approximate Floating Point Unit"

From iis-projects

(Created page with "thumb ==Short Description== ''Floating point units'' (FPU) are one part of a micro-processor and usually directly connected in th...") |

|||

| (7 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | [[File: | + | [[File:fpudesign.jpg|400px|right|thumb]] |

==Short Description== | ==Short Description== | ||

| − | ''Floating point units'' (FPU) are one part of a micro-processor and usually directly | + | ''Floating point units'' (FPU) are one part of a micro-processor and usually directly integrated in the pipeline. In a multi-processor environment one private FPU per processor core is not the most energy efficient implementation because ''floating point'' (FP)-operations are not always used which means they remain idle for lots of cycles. Sharing FPUs among the processors is expected to improve the utilization of the FPUs and therefore reduce the overall power consumption of the system. Sharing FPUs allows to employ several different units, which can be either precise or approximate. |

| − | An approximate FPU benefits of a faster | + | An approximate FPU benefits of a smaller design, a faster and low-power execution and is a promising approach to further improve the energy efficiency of the system. One way to approximate FP-operations is to use Newton's method to compute FP-operations in an iterative manner. A very fast first order approximation using a look-up table is already sufficient for many applications and greatly simplifies the design. |

Your task will be to establish a matlab framework to evaluate different algorithms to approximate FP-operations and finally implement the preferred algorithm in hardware such that it can be integrated in the multi-processor platform. | Your task will be to establish a matlab framework to evaluate different algorithms to approximate FP-operations and finally implement the preferred algorithm in hardware such that it can be integrated in the multi-processor platform. | ||

| − | ===Status: | + | ===Status: Completed === |

| − | : | + | : Fall Semester 2014 (sem14h1) |

| − | : | + | : Youri Popoff, Florian Scheidegger, Lukas Mueller, Thomas Gautschi, Mario Burger, Fabian Schuiki |

===Prerequisites=== | ===Prerequisites=== | ||

| Line 21: | Line 21: | ||

: 25% EDA tools | : 25% EDA tools | ||

| + | ===Professor=== | ||

| + | : [http://www.iis.ee.ethz.ch/portrait/staff/lbenini.en.html Luca Benini] | ||

| + | <!-- : [http://www.iis.ee.ethz.ch/portrait/staff/huang.en.html Qiuting Huang] ---> | ||

| + | <!-- : [http://lne.ee.ethz.ch/en/general-information/people/professor.html Vanessa Wood] ---> | ||

| + | <!-- : [http://www.iis.ee.ethz.ch/portrait/staff/mluisier.en.html Mathieu Luisier] ---> | ||

| + | <!-- : [http://www.iis.ee.ethz.ch/portrait/staff/schenk.en.html Andreas Schenk] ---> | ||

| + | <!-- : [http://www.dz.ee.ethz.ch/en/general-information/about/staff/uid/364.html Hubert Kaeslin] ---> | ||

[[#top|↑ top]] | [[#top|↑ top]] | ||

| + | ==Detailed Task Description== | ||

| − | [[Category:Digital]] [[Category:Semester Thesis]] [[Category: | + | ===Goals=== |

| + | ===Practical Details=== | ||

| + | * '''[[Project Plan]]''' | ||

| + | * '''[[Project Meetings]]''' | ||

| + | * '''[[Design Review]]''' | ||

| + | * '''[[Coding Guidelines]]''' | ||

| + | * '''[[Final Report]]''' | ||

| + | * '''[[Final Presentation]]''' | ||

| + | |||

| + | ==Results== | ||

| + | |||

| + | |||

| + | [[Category:Digital]] [[Category:Semester Thesis]] [[Category:Completed]] [[Category:UlpSoC]] [[Category:2014]] [[Category:ASIC]] [[Category:PULP]] | ||

| + | [[Category:Acceleration and Transprecision]] [[Category:Fschuiki]] | ||

Latest revision as of 10:58, 21 February 2018

Contents

Short Description

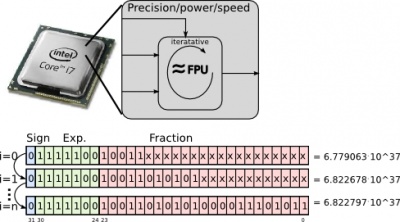

Floating point units (FPU) are one part of a micro-processor and usually directly integrated in the pipeline. In a multi-processor environment one private FPU per processor core is not the most energy efficient implementation because floating point (FP)-operations are not always used which means they remain idle for lots of cycles. Sharing FPUs among the processors is expected to improve the utilization of the FPUs and therefore reduce the overall power consumption of the system. Sharing FPUs allows to employ several different units, which can be either precise or approximate.

An approximate FPU benefits of a smaller design, a faster and low-power execution and is a promising approach to further improve the energy efficiency of the system. One way to approximate FP-operations is to use Newton's method to compute FP-operations in an iterative manner. A very fast first order approximation using a look-up table is already sufficient for many applications and greatly simplifies the design.

Your task will be to establish a matlab framework to evaluate different algorithms to approximate FP-operations and finally implement the preferred algorithm in hardware such that it can be integrated in the multi-processor platform.

Status: Completed

- Fall Semester 2014 (sem14h1)

- Youri Popoff, Florian Scheidegger, Lukas Mueller, Thomas Gautschi, Mario Burger, Fabian Schuiki

Prerequisites

- VLSI I

- Interest in Computer Architectures

- Matlab and VHDL/System Verilog knowledge

Character

- 25% Theory

- 50% ASIC Design

- 25% EDA tools