Difference between revisions of "Design of low-offset dynamic comparators"

From iis-projects

(→Status: Hide) |

|||

| Line 48: | Line 48: | ||

==Links== | ==Links== | ||

[[Category:Analog]] | [[Category:Analog]] | ||

| − | [[Category: | + | [[Category:Completed]] |

| − | |||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

Latest revision as of 17:35, 21 December 2017

Contents

Short Description

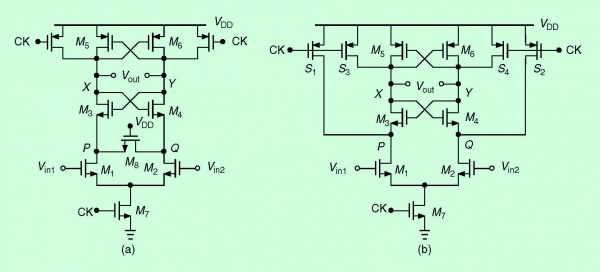

Low-power consumption is a common requirement for all circuits running in autonomous systems. Many such circuits contain comparators, e.g. for event detection. When the power budget is low then comparators that are always on are usually slow and exhibit too much noise. When a system clock is available dynamic comparators are an attractive alternative, as they can use higher current and therefore less noise at the moment of decision when it counts, but only for a short time. They therefore can reach much lower average power consumption than class A operated comparators with similar delay time (determined by the clock period). In this thesis different topologies will be compared to each other for resolution, offset, noise and power consumption

Status: Available

- Looking for 1-2 Semester students

- Contact: Thomas Burger

Prerequisites

- AIC

Character

- 20% Theory

- 80% Circuit Design