Difference between revisions of "EvalEDGE: A 2G Cellular Transceiver FMC"

From iis-projects

(Created page with "thumb|RazorEDGE ASIC with testbed. ===Date=== : 2014 ===Personnel=== : Harald Kroell : Stefan Zwicky : User:Webe...") |

|||

| (6 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

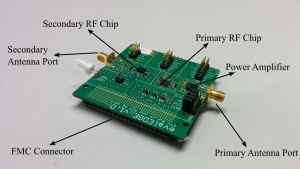

| − | [[File: | + | [[File:evalEDGE.jpg|thumb|The evalEDGE 2G cellular transceiver FMC module.]] |

| + | [[File:2G_testbed.jpg|thumb|Testbed setup with L2/L3 processing on ZedBoard (top), double RF on evalEDGE v1.0 (middle), and DBB on ML605 (bottom).]] | ||

===Date=== | ===Date=== | ||

| Line 5: | Line 6: | ||

===Personnel=== | ===Personnel=== | ||

| − | : [[User:Weberbe| | + | : [[User:Weberbe|Benjamin Weber]] |

: Stefan Zwicky | : Stefan Zwicky | ||

| − | : [[User: | + | : [[User:Kroell|Harald Kroell]] |

| − | |||

| − | |||

===Funding=== | ===Funding=== | ||

| − | : | + | : [http://www.haslerstiftung.ch/ Hasler Stiftung] |

| − | : Hasler Stiftung | ||

===Partners=== | ===Partners=== | ||

| − | : [http://www.newacp.ch ACP AG] | + | : [http://www.newacp.ch/ ACP AG] |

===Summary=== | ===Summary=== | ||

| − | The | + | The PCB board ''evalEDGE'' is an FPGA Mezzanine Card (FMC) module with RF support for 2G cellular communication. It holds 2 RF transceiver chips, a power amplifier, and power control logic. The RF transceivers can be configured jointly or independently to support receive diversity and downlink dual carrier scenarios, respectively. The evalEDGE FMC module was used jointly with a ZedBoard and an ML605 for receiver characterization in [1]. The evalEDGE board itself has been published in [2]. The current evalEDGE version is v1.0. However, it has been superseded by the [[evaLTE]] board, which offers not only 2G but also 3G and 4G transceiver functionality. |

| − | transceiver | ||

| − | and | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

===Publications=== | ===Publications=== | ||

| − | + | [1] H. Kröll, S. Zwicky, B. Weber, C. Roth, D. Tschopp, C. Benkeser, A. Burg, and Q. Huang, "An Evolved GSM/EDGE Baseband ASIC Supporting Rx Diversity," ''Solid-State Circuits, IEEE Journal of'', vol. 50, no. 7, pp. 1690–1701, July 2015. [http://dx.doi.org/10.1109/JSSC.2015.2417802 DOI: 10.1109/JSSC.2015.2417802] | |

| + | |||

| + | [2] B. Weber, H. Kröll, S. Altorfer, and Q. Huang, "Cellular Baseband Development Platform with an open RF Interface," in ''2015 Wireless Innovation Forum European Conference on Communications Technologies and Software Defined Radio (WInnComm-Europe 2015)'', Erlangen, Germany, Oct. 2015, pp. 26–30. | ||

===Links=== | ===Links=== | ||

| − | * [http:// | + | * [http://www.vita.com/fmc FMC Marketing Alliance] |

| + | * [http://www.xilinx.com/products/boards-and-kits/ek-v6-ml605-g.html ML605] | ||

| + | * [http://zedboard.org/product/zedboard ZedBoard] | ||

[[Category:Digital]] | [[Category:Digital]] | ||

[[Category:Research]] | [[Category:Research]] | ||

[[Category:Completed]] | [[Category:Completed]] | ||

| − | [[Category: | + | [[Category:2014]] |

[[Category:Telecommunications]] | [[Category:Telecommunications]] | ||

| − | [[Category: | + | [[Category:PCB]] |

[[Category:Weberbe]] | [[Category:Weberbe]] | ||

[[Category:Kroell]] | [[Category:Kroell]] | ||

Latest revision as of 17:10, 17 December 2015

Date

Personnel

- Benjamin Weber

- Stefan Zwicky

- Harald Kroell

Funding

Partners

Summary

The PCB board evalEDGE is an FPGA Mezzanine Card (FMC) module with RF support for 2G cellular communication. It holds 2 RF transceiver chips, a power amplifier, and power control logic. The RF transceivers can be configured jointly or independently to support receive diversity and downlink dual carrier scenarios, respectively. The evalEDGE FMC module was used jointly with a ZedBoard and an ML605 for receiver characterization in [1]. The evalEDGE board itself has been published in [2]. The current evalEDGE version is v1.0. However, it has been superseded by the evaLTE board, which offers not only 2G but also 3G and 4G transceiver functionality.

Publications

[1] H. Kröll, S. Zwicky, B. Weber, C. Roth, D. Tschopp, C. Benkeser, A. Burg, and Q. Huang, "An Evolved GSM/EDGE Baseband ASIC Supporting Rx Diversity," Solid-State Circuits, IEEE Journal of, vol. 50, no. 7, pp. 1690–1701, July 2015. DOI: 10.1109/JSSC.2015.2417802

[2] B. Weber, H. Kröll, S. Altorfer, and Q. Huang, "Cellular Baseband Development Platform with an open RF Interface," in 2015 Wireless Innovation Forum European Conference on Communications Technologies and Software Defined Radio (WInnComm-Europe 2015), Erlangen, Germany, Oct. 2015, pp. 26–30.