Difference between revisions of "Fast Wakeup From Deep Sleep State"

From iis-projects

(Created page with "==Short Description== 600px|thumb|right|Architecture with reusable IPs highlighted Ultra-low power operation and extreme energy efficiency are str...") |

|||

| Line 1: | Line 1: | ||

==Short Description== | ==Short Description== | ||

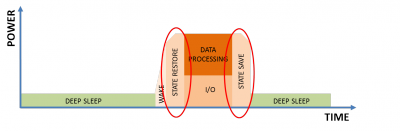

| − | [[File:Ap fulmine arch.png| | + | [[File:Ap iot pattern.png|400px|thumb|right|Typical IoT power cycle]] |

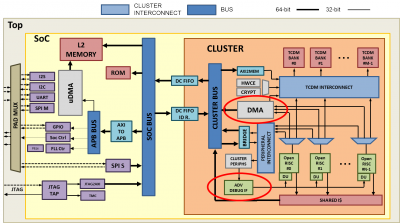

| + | [[File:Ap fulmine arch.png|400px|thumb|right|Architecture with reusable IPs highlighted]] | ||

Ultra-low power operation and extreme energy efficiency are strong requirements for a number of high-growth application areas, such as E-health, Internet of Things, and wearable Human-Computer Interfaces. | Ultra-low power operation and extreme energy efficiency are strong requirements for a number of high-growth application areas, such as E-health, Internet of Things, and wearable Human-Computer Interfaces. | ||

Most of the applications do not need an always-on system and often implement aggressive duty cycling to minimize the average power consumption. In such applications optimizing the wakeup energy consumption has a significant impact on the overall energy drawn from the battery. | Most of the applications do not need an always-on system and often implement aggressive duty cycling to minimize the average power consumption. In such applications optimizing the wakeup energy consumption has a significant impact on the overall energy drawn from the battery. | ||

The goal of the project is to implement an hardware IP to enable fast save and restore of the status of the PULP multicore platform reusing as much as possible existing components. | The goal of the project is to implement an hardware IP to enable fast save and restore of the status of the PULP multicore platform reusing as much as possible existing components. | ||

The project can be summarized as follows: | The project can be summarized as follows: | ||

| − | + | -Extend the current debug unit and enable its access from the system interconnect | |

| − | + | -implement a state machine that controls the system DMA to save/restore data stored in L1 data memory | |

| − | + | -design the controller to save and restore both core and L1 memory. | |

| − | + | -validate the design and include save/restore checks in the regression infrastructure | |

===Status: Available === | ===Status: Available === | ||

| Line 17: | Line 18: | ||

===Character=== | ===Character=== | ||

| − | : | + | : 20% Embedded programming |

| − | : 40% | + | : 40% HW design |

| + | : 40% System validation | ||

===Requirements=== | ===Requirements=== | ||

| − | Knowledge of | + | Knowledge of C/C++ |

| − | VHDL | + | VHDL or Verilog HDL |

==Links== | ==Links== | ||

Revision as of 16:49, 14 April 2016

Contents

Short Description

Ultra-low power operation and extreme energy efficiency are strong requirements for a number of high-growth application areas, such as E-health, Internet of Things, and wearable Human-Computer Interfaces. Most of the applications do not need an always-on system and often implement aggressive duty cycling to minimize the average power consumption. In such applications optimizing the wakeup energy consumption has a significant impact on the overall energy drawn from the battery. The goal of the project is to implement an hardware IP to enable fast save and restore of the status of the PULP multicore platform reusing as much as possible existing components. The project can be summarized as follows:

-Extend the current debug unit and enable its access from the system interconnect -implement a state machine that controls the system DMA to save/restore data stored in L1 data memory -design the controller to save and restore both core and L1 memory. -validate the design and include save/restore checks in the regression infrastructure

Status: Available

- Semester/Master Thesis

- Supervision: Antonio Pullini (IIS)

Professor

Character

- 20% Embedded programming

- 40% HW design

- 40% System validation

Requirements

Knowledge of C/C++ VHDL or Verilog HDL