Difference between revisions of "Fault-Tolerant Floating-Point Units (M)"

From iis-projects

| Line 4: | Line 4: | ||

[[Category:Acceleration_and_Transprecision]] | [[Category:Acceleration_and_Transprecision]] | ||

[[Category:High Performance SoCs]] | [[Category:High Performance SoCs]] | ||

| + | [[Category:Fault Tolerance]] | ||

| + | [[Category:HW/SW Safety and Security]] | ||

[[Category:Computer Architecture]] | [[Category:Computer Architecture]] | ||

[[Category:2023]] | [[Category:2023]] | ||

Revision as of 14:50, 13 November 2023

Contents

Overview

Status: Available

- Type: Master Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

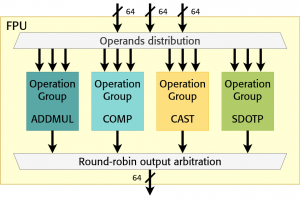

Fault-tolerant features are crucial in critical and hostile environments (automotive, space, …). The goal of this project is to enhance the FP unit (FPU) developed at IIS [1] with fault-tolerant features (such as redundancy schemes [2]).

Character

- 20% Literature / architecture review

- 40% RTL implementation

- 40% Evaluation

Prerequisites

- Strong interest in computer architecture

- Experience with digital design in SystemVerilog as taught in VLSI I

- Experience with ASIC implementation flow (synthesis) as taught in VLSI II