Integrated Information Processing

From iis-projects

Integrated Information Processing Group

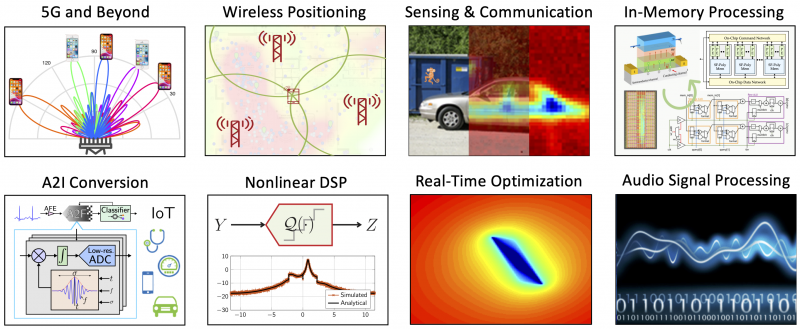

The Integrated Information Processing (IIP) Group carries out research in the following areas:

Theory, Algorithms, and Hardware for Beyond 5G

The main focus of the IIP Group is on theory, algorithm design, and hardware implementation of new technologies for beyond fifth-generation (5G) wireless communication systems. The projects in this area focus on emerging communication technologies including massive MIMO, millimeter-wave (mmWave) and terahertz communication, cell-free massive MIMO, intelligent reflective surfaces, ultra low-latency short-packet transmission, and testbed design for massive MIMO prototyping.

Positioning with Wireless Signals

Indoor positioning and outdoor positioning in urban scenarios of mobile phones is a notoriously difficult task. Recently, tools from machine learning have been used to perform positioning from channel-state information (CSI). The projects in this area focus on channel charting, a new technology developed in the IIP group that enables self-supervised positioning from CSI without the users' consent.

Simultaneous Sensing and Communication

Modern wireless systems are equipped with large arrays of parallel radio-frequency (RF) chains. Such RF chains are extremely accurate sensors that can be used not only for high-rate data transmission but also for sensing. The projects in the emerging area of simultaneous sensing and communication (SISCO) are on imaging the area next to the antenna array and on classification of user behavior using machine learning techniques.

All-Digital In-Memory Processing

Processing in memory (PIM) moves computation into memories with the goal of improving throughput and energy-efficiency compared to traditional von Neumann-based architectures. The projects in this area are in designing all-digital and semi-custom PIM accelerators (application-specific integrated circuits) that can be fabricated with conventional CMOS technologies and for emerging applications in machine learning, signal processing, and wireless communication.

Analog-to-Information Conversion for Low-Power Sensing

Always-on sensors that continuously monitor the environment for certain events must operate with energy-efficient classification and detection pipelines. The projects in this area build upon a novel classification pipeline developed in the IIP group called analog-to-feature (A2F) conversion that directly acquires features in the analog domain using non-uniform wavelet sampling (NUWS). Possible applications are real-time sensing and classification of EEG, ECG, RF, and audio signals.

Available Projects

Theory, Algorithms, and Hardware for Beyond 5G

- ASIC implementation of a beamspace massive MIMO-OFDM detector for 5G/6G

- Analysis of Low-Power Wide Area Network Technologies for the Internet of Things

- Low-Complexity MIMO Detection

- Low-power time synchronization for IoT applications

- Forward error-correction ASIC using GRAND

- Reconfigurable Fully-Unrolled 2D-FFT Core Generator for Multi-Antenna mmWave Communication

- Low Resolution Neural Networks

- VLSI Design of an Asynchronous LDPC Decoder

- FFT HDL Code Generator for Multi-Antenna mmWave Communication

- Low-Resolution 5G Beamforming Codebook Design

- Practical Reconfigurable Intelligent Surfaces (RIS)

- Peak-to-average power Reduction

Positioning with Wireless Signals

- Self-Supervised User Positioning in Cell-Free Massive MIMO Systems

- Signal Acquisition and Clock Offset Compensation for High-Rate Pulse UWB PHYs

Simultaneous Sensing and Communication

- Through Wall Radar Imaging using Machine Learning

- Passive Radar for UAV Detection using Machine Learning

All-Digital In-Memory Processing

- Accelerating Applications Relying on Matrix-Vector-Product-Like Operations

- XNORLAX: Fused XNOR-LATCH Custom-Standard-Cell-Based Processing-in-Memory

- Design-Space Exploration of Low-Resolution Matrix-Vector Multipliers