Difference between revisions of "IoT Turbo Decoder"

From iis-projects

| Line 11: | Line 11: | ||

Your task during this project is to implement a Turbo Decoder for LTE Category M1. A Matlab framework exists, which allows the verify the performance of your design. Then you will implement it as part of an existing modem platform including RISC-V processor cluster in Stratus HLS or VHDL. The main design objectives are a good energy efficiency and a low area footprint. One way to reduce the area is the sharing of memory with the processor cluster. The final design can either be mapped to an FPGA, or an ASIC. | Your task during this project is to implement a Turbo Decoder for LTE Category M1. A Matlab framework exists, which allows the verify the performance of your design. Then you will implement it as part of an existing modem platform including RISC-V processor cluster in Stratus HLS or VHDL. The main design objectives are a good energy efficiency and a low area footprint. One way to reduce the area is the sharing of memory with the processor cluster. The final design can either be mapped to an FPGA, or an ASIC. | ||

| + | <!-- | ||

===Status: Available === | ===Status: Available === | ||

: Looking for 1-2 Semester/Master students | : Looking for 1-2 Semester/Master students | ||

| Line 16: | Line 17: | ||

===Prerequisites=== | ===Prerequisites=== | ||

: VLSI I | : VLSI I | ||

| + | ---> | ||

<!-- | <!-- | ||

===Status: Completed === | ===Status: Completed === | ||

| Line 21: | Line 23: | ||

: Matthias Baer, Renzo Andri | : Matthias Baer, Renzo Andri | ||

---> | ---> | ||

| − | + | ||

===Status: In Progress === | ===Status: In Progress === | ||

| − | : | + | : Raphaela Eberli |

| − | : Supervision: [[:User:Lstefan | Stefan Lippuner]] | + | : Supervision: [[:User:Lstefan | Stefan Lippuner]], [[:User:Msalomon | Mauro Salomon]] |

| − | + | ||

===Character=== | ===Character=== | ||

: 20% Theory, Algorithms and Simulation | : 20% Theory, Algorithms and Simulation | ||

Revision as of 17:16, 9 March 2018

Contents

Introduction

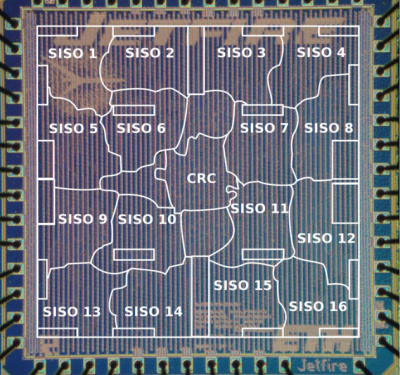

In wireless communication, forward error correction is used to reliably transmit data. Cellular standards, like LTE, have used Turbo Codes for this purpose. They are able to approach the channel capacity by processing the received data iteratively. Several Turbo Decoders have been developed at IIS in the past (e.g.), which were mainly focused on achieving the high throughput required for LTE.

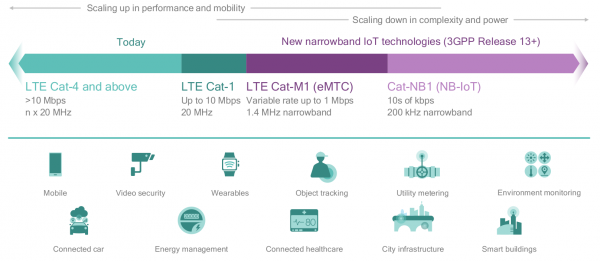

In order to optimize cellular communication for the IoT, a new variant of LTE have been standardized as part of Release 13 in 2016: LTE Cat-M1 (eMTC). This category offers only a reduced throughput of 300 kbps, but instead focuses on improved coverage, better battery life and lower cost. As part of our communication platform, we are currently developing a modem, which supports LTE Cat-M1, at IIS.

Project Description

Your task during this project is to implement a Turbo Decoder for LTE Category M1. A Matlab framework exists, which allows the verify the performance of your design. Then you will implement it as part of an existing modem platform including RISC-V processor cluster in Stratus HLS or VHDL. The main design objectives are a good energy efficiency and a low area footprint. One way to reduce the area is the sharing of memory with the processor cluster. The final design can either be mapped to an FPGA, or an ASIC.

Status: In Progress

- Raphaela Eberli

- Supervision: Stefan Lippuner, Mauro Salomon

Character

- 20% Theory, Algorithms and Simulation

- 30% Architecture Design

- 50% Hardware Implementation (HLS/VHDL)

Professor

Related Projects

RF SoCs for the Internet of Things

References

[1] 3GPP. Release 13. http://www.3gpp.org/release-13, 2016.

[2] Qualcomm. Paving the path to Narrowband 5G with LTE Internet of Things (IoT), 2016