Difference between revisions of "Power Optimization in Multipliers"

From iis-projects

| Line 48: | Line 48: | ||

[[Category:In progress]] | [[Category:In progress]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

| − | + | [[Category:Felber]] | |

<!-- | <!-- | ||

Revision as of 20:04, 17 February 2015

Contents

Short Description

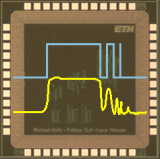

Multipliers are often the largest and most power consuming units in the datapath of an ASIC. Depending on the application the data samples can have a rather small dynamic range so that the upper bits toggle very rarely. Many publications have proposed multiplier implementations that shut certain unused parts of the multiplier off when inputs to not change in order to save dynamic power. Most of these techniques are based on efficient transistor-level structures that allow dynamic range detection and multiplier re-configuration with little hardware overhead and speed penalty. Such techniques however are not compatible with standard-cell technologies. The goal of this project is to assess existing and investigate new techniques for dynamic power optimization in multipliers with low-activity inputs that can be implemented with standard-cells and that can be automated in order to be used in a synthesis-based flow.

This project will be done in collaboration with Synopsys.

Status: In Progress

- Haralds Capkevics

- Supervision: Norbert Felber

Prerequisites

- VLSI I

- VLSI II (recommended)

- Interest in Electronic Design automation (EDA)

Character

- 20% Theory

- 40% ASIC/ Digital Circuit Design

- 40% EDA tools