Difference between revisions of "Radiation Testing of a PULP ASIC"

From iis-projects

| (7 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

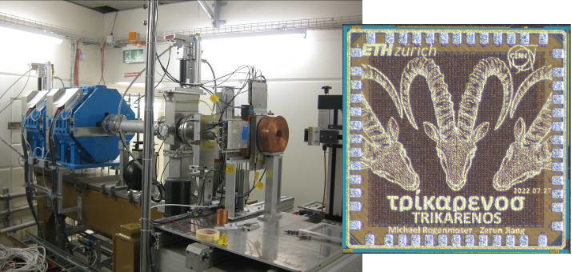

| + | [[File:trik_rad_test.png|800px|thumb|PSI proton irradiation facility and the Trikarenos SoC.]] | ||

| + | |||

<!-- Radiation Testing of a PULP ASIC (1S) --> | <!-- Radiation Testing of a PULP ASIC (1S) --> | ||

| Line 4: | Line 6: | ||

[[Category:Fault Tolerance]] | [[Category:Fault Tolerance]] | ||

[[Category:HW/SW Safety and Security]] | [[Category:HW/SW Safety and Security]] | ||

| − | [[Category: | + | [[Category:2023]] |

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

[[Category:Michaero]] | [[Category:Michaero]] | ||

| − | [[Category: | + | [[Category:Lrufer]] |

| + | [[Category:In progress]] | ||

| Line 13: | Line 16: | ||

In this thesis, you will design an experiment that will run under a proton beam to measure the efficiency of radiation hardening techniques we have added to our RISC-V based PULP systems in a couple of recent ASIC designs. Your work will be to establish an efficient method to determine the failure rates of systems with and without different fault tolerance mechanisms between a test board under the beam and a controlling system (realized for example using a Raspberry Pi board) in the same room. As access to the room will be limited during the experiment, the system should be designed to allow us to sample as much data as possible during the short window in which we will have access to the facilities. | In this thesis, you will design an experiment that will run under a proton beam to measure the efficiency of radiation hardening techniques we have added to our RISC-V based PULP systems in a couple of recent ASIC designs. Your work will be to establish an efficient method to determine the failure rates of systems with and without different fault tolerance mechanisms between a test board under the beam and a controlling system (realized for example using a Raspberry Pi board) in the same room. As access to the room will be limited during the experiment, the system should be designed to allow us to sample as much data as possible during the short window in which we will have access to the facilities. | ||

| − | While exact dates are not known, it is expected that the real experiment will take place in | + | While exact dates are not known, it is expected that the real experiment will take place in October-December time frame, and it will be possible to join the experiment on site. |

| − | == Status: | + | == Status: In Progress == |

* Type: Semester Thesis | * Type: Semester Thesis | ||

| Line 20: | Line 23: | ||

* Supervisors: | * Supervisors: | ||

** [[:User:Michaero | Michael Rogenmoser]]: [mailto:michaero@iis.ee.ethz.ch michaero@iis.ee.ethz.ch] | ** [[:User:Michaero | Michael Rogenmoser]]: [mailto:michaero@iis.ee.ethz.ch michaero@iis.ee.ethz.ch] | ||

| + | ** [[:User:Lrufer | Luca Rufer]]: [mailto:lrufer@iis.ee.ethz.ch lrufer@iis.ee.ethz.ch] | ||

** [[:User:Kgf | Frank Gurkaynak]]: [mailto:kgf@iis.ee.ethz.ch kgf@iis.ee.ethz.ch] | ** [[:User:Kgf | Frank Gurkaynak]]: [mailto:kgf@iis.ee.ethz.ch kgf@iis.ee.ethz.ch] | ||

Latest revision as of 14:59, 25 October 2023

Contents

Overview

In this thesis, you will design an experiment that will run under a proton beam to measure the efficiency of radiation hardening techniques we have added to our RISC-V based PULP systems in a couple of recent ASIC designs. Your work will be to establish an efficient method to determine the failure rates of systems with and without different fault tolerance mechanisms between a test board under the beam and a controlling system (realized for example using a Raspberry Pi board) in the same room. As access to the room will be limited during the experiment, the system should be designed to allow us to sample as much data as possible during the short window in which we will have access to the facilities.

While exact dates are not known, it is expected that the real experiment will take place in October-December time frame, and it will be possible to join the experiment on site.

Status: In Progress

- Type: Semester Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

At IIS, we recently taped out two ASICs with features for fault tolerance, increasing redundancy to radiation-induced errors, e.g. for Space applications.

After these Chips (Cerberus and Trikarenos) are brought up once they return from being manufactured, we would like to test them under a radiation beam.

Project

In this project, an independent testing infrastructure for the two chips will be developed, allowing for testing in a sealed chamber under a radiation beam. As this chamber only provides limited access, a reliable stand-alone infrastructure is required. This includes:

- An overall test setup, picking the devices to control and interface with the chips

- software for a simple computer to reliably control and program the chip, and log any errors

- Time-permitting, a PCB for the chips, providing power and clock and interface options

As the chips are not back from manufacturing yet, the testing infrastructure will initially be deployed with an FPGA port of the chip for debugging.

Character

- 30% System design

- 50% Software design (scripting, C, python)

- 20% PCB design

Prerequisites

- Familiarity with ASIC design and testing is beneficial

- Experience with PCB design is beneficial