Difference between revisions of "Shared Correlation Accelerator for an RF SoC"

From iis-projects

| Line 17: | Line 17: | ||

| − | + | ===Status: Available === | |

| − | : Looking for 1 | + | : Looking for 1 Semester student |

: Contact: [[:User:Lstefan | Stefan Lippuner]] | : Contact: [[:User:Lstefan | Stefan Lippuner]] | ||

| − | |||

===Prerequisites=== | ===Prerequisites=== | ||

: VLSI I | : VLSI I | ||

| Line 29: | Line 28: | ||

: Matthias Baer, Renzo Andri | : Matthias Baer, Renzo Andri | ||

---> | ---> | ||

| + | <!-- | ||

===Status: In Progress === | ===Status: In Progress === | ||

: Student: Sascha Giger | : Student: Sascha Giger | ||

: Supervision: [[:User:Lstefan | Stefan Lippuner]] | : Supervision: [[:User:Lstefan | Stefan Lippuner]] | ||

| + | ---> | ||

===Character=== | ===Character=== | ||

| Line 63: | Line 64: | ||

[[Category:FPGA]] | [[Category:FPGA]] | ||

[[Category:Telecommunications]] | [[Category:Telecommunications]] | ||

| − | [[Category: | + | [[Category:Available]] |

[[Category:Hot]] | [[Category:Hot]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

| Line 69: | Line 70: | ||

<!-- | <!-- | ||

| + | #[[Category:In progress]] | ||

Revision as of 13:26, 4 December 2017

Contents

Introduction

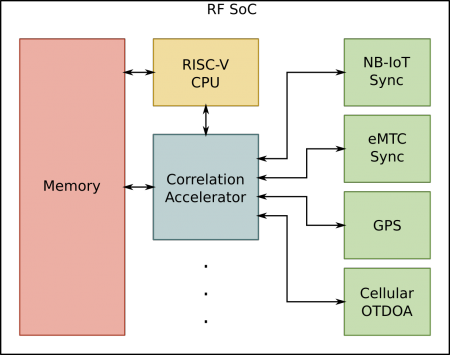

We are currently working on designing Radio Frequency (RF) Systems on a chip (SoCs) for the Internet of Things (IoT). Requirements for these devices often include data connectivity and location information. A drone may, for instance, use both GPS and cellular positioning to increase the accuracy of the location estimate. We want to integrate both functionalities on a single chip.

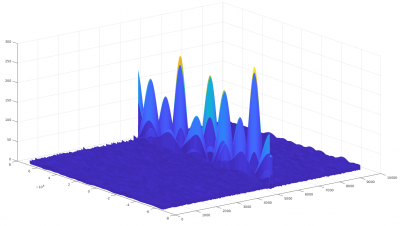

Positioning and network synchronization rely on performing a large number of cross-correlations in real-time. Due to the large throughput requirements, large accelerators are required. Instead of using a dedicated circuit for each standard, we would like to share a single, flexible accelerator for all these tasks.

Project Description

The goal of this project is, to develop a shared correlation accelerator for our RF SoC. This unit should support both positioning, as well as the synchronization for NB-IoT and eMTC. To do this, you will study the algorithms to quickly calculate a large number of cross-correlations. Using this knowledge, you will develop the accelerator in VHDL, or using High-Level Synthesis (HLS). It should be able to meet the throughput requirements of 100M correlation results/s, while keeping the area as low as possible.

Once you have implemented and verified the unit, you may tape out your own chip, or test it in our FPGA testbed.

Status: Available

- Looking for 1 Semester student

- Contact: Stefan Lippuner

Prerequisites

- VLSI I

- VLSI II/III (for an ASIC tapeout)

Character

- 20% Theory, Algorithms and Simulation

- 50% Implementation (HLS/VHDL)

- 30% ASIC Implementation / FPGA Integration