Difference between revisions of "Successive Approximation Register (SAR) ADC"

From iis-projects

(Created page with "thumb|300px ==Short Description== Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to ...") |

|||

| (One intermediate revision by one other user not shown) | |||

| Line 1: | Line 1: | ||

| − | [[File:Successive Approximation Register DAC.png|thumb| | + | [[File:Successive Approximation Register DAC.png|thumb|400px]] |

==Short Description== | ==Short Description== | ||

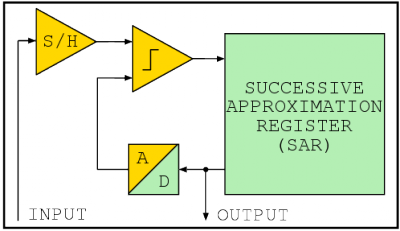

Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to high resolution low-power applications, such as battery powered systems. Their architecture consists of a front-end sample-and-hold (S/H), a comparator, a decision register, and a DAC. The ADC employs a binary search algorithm to perform the conversion. This project consists of building a MATLAB model, analyzing the different circuits of the ADC, and designing and implementing a high-resolution slowly clocked SAR converter. | Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to high resolution low-power applications, such as battery powered systems. Their architecture consists of a front-end sample-and-hold (S/H), a comparator, a decision register, and a DAC. The ADC employs a binary search algorithm to perform the conversion. This project consists of building a MATLAB model, analyzing the different circuits of the ADC, and designing and implementing a high-resolution slowly clocked SAR converter. | ||

| Line 46: | Line 46: | ||

==Links== | ==Links== | ||

[[Category:Analog]] | [[Category:Analog]] | ||

| − | |||

| − | |||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

Latest revision as of 17:43, 21 December 2017

Contents

Short Description

Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to high resolution low-power applications, such as battery powered systems. Their architecture consists of a front-end sample-and-hold (S/H), a comparator, a decision register, and a DAC. The ADC employs a binary search algorithm to perform the conversion. This project consists of building a MATLAB model, analyzing the different circuits of the ADC, and designing and implementing a high-resolution slowly clocked SAR converter.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Schekeb Fateh

Prerequisites

- AIC

Character

- 20% Theory

- 80% Circuit Design