Difference between revisions of "Synchronization and Power Control Concepts for 3GPP TD-SCDMA"

From iis-projects

(Created page with "thumb|600px ==Short Description== TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptiv...") |

m |

||

| Line 8: | Line 8: | ||

: Looking for 1-2 Semester/Master students | : Looking for 1-2 Semester/Master students | ||

: Contact: [http://iis-projects.ee.ethz.ch/index.php/User:Badawi Karim Badawi] | : Contact: [http://iis-projects.ee.ethz.ch/index.php/User:Badawi Karim Badawi] | ||

| − | === | + | ===Prerequisites=== |

: VLSI I | : VLSI I | ||

: Interest in Mobile Communications | : Interest in Mobile Communications | ||

| Line 51: | Line 51: | ||

==Links== | ==Links== | ||

| + | |||

| + | [[#top|↑ top]] | ||

| + | |||

[[Category:Digital]] | [[Category:Digital]] | ||

[[Category:Available]] | [[Category:Available]] | ||

Revision as of 10:26, 17 January 2014

Contents

Short Description

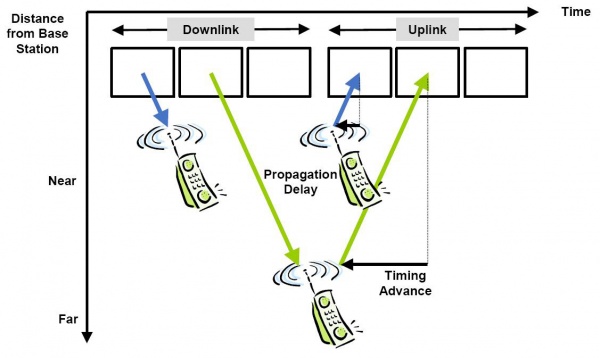

TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptive CDMA component operating in a synchronous mode. Its TDD nature allows to master asymmetric services more efficiently than other 3G standards. Up- and downlink resources are flexibly assigned according to traffic needs, which is helpful in an environment with increasing data traffic, which tends to be asymmetric (mobile Internet).

In order to meet these promises, a highly synchronised power-controlled transmission is eminent. Hence, TD-SCDMA utilize a 4-level synchronisation in Time and Frequency (chip, bit, slot and frame levels). In this thesis, fast synchronisation and power control techniques shall be investigated focusing on their performance-complexity tradeoff and their convergence speed. Therefore, Matlab blocks have to be implemented and integrated within our TD-SCDMA simulation chain, followed by implementation in VHDL code, synthesis and design optimization.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Karim Badawi

Prerequisites

- VLSI I

- Interest in Mobile Communications

- Matlab and VHDL knowledge

Character

- 25% Theory

- 25% Simulation

- 25% Architecture/VHDL

- 25% ASIC Implementation