Difference between revisions of "Turbo Decoder Design for High Code Rates"

From iis-projects

(Created page with "File:Turbo Decoder Design for High Code Rates.png|thumb|560px|The impact of code rate on throughput and memory capacity of traditional acquisition-run-based turbo decoders (...") |

(→Personnel) |

||

| Line 5: | Line 5: | ||

===Personnel=== | ===Personnel=== | ||

| − | : [[:User:Rothc| | + | : [[:User:Rothc|Christoph Roth]] |

: Christian Benkeser | : Christian Benkeser | ||

Revision as of 10:26, 4 February 2014

Date

Personnel

- Christoph Roth

- Christian Benkeser

Funding

- Hasler Foundation

- KTI SharperEDGE

Partners

Summary

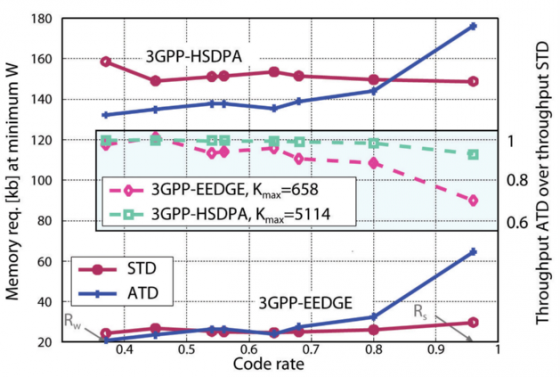

Link adaptation and hybrid-ARQ are key features of modern mobile communication standards, that considerably increase average throughput. In order to allow for an efficient use of radio resources in varying transmission environments, both features rely on high-performance error-correction codes with variable code-block sizes and code rates. In particular, recent mobile cellular standards in the 3GPP standard suite, such as Evolved EDGE, HSPA or LTE, specify powerful turbo codes with code-block sizes of several hundred or thousand bits, and varying code rates ranging from 0.33 up to 1. Transmission modes with very high code rates have been proved crucial for throughput optimization in low- and medium-SNR conditions in conjunction with hybrid-ARQ.

Hence, the emerging importance of high code rates in modern mobile communication systems calls for turbo-decoder solutions that achieve optimum performance over the entire range of specified code rates. In this project, we have thoroughly analyzed the impact of very high code rates on the VLSI design of turbo decoders. Based on the sliding-window BCJR decoding algorithm we have compared two approaches to initialize the window boundaries. We have found that the traditional one (widely employed in practice) is highly sensitive to the code rate, and that corresponding implementations are clearly outperformed in terms of silicon area and power consumption by implementations relying on the alternative approach when the entire range of code rates has to be supported.

Publications

- C. Benkeser, C. Roth, Q. Huang, "Turbo Decoder Design for High Code Rates", IEEE/IFIP International Conference on Very Large Scale Integration (VLSI-SoC), Santa Cruz, USA, 7-10 Oct 2012