Variability Tolerant Ultra Low Power Cluster

From iis-projects

Contents

Short Description

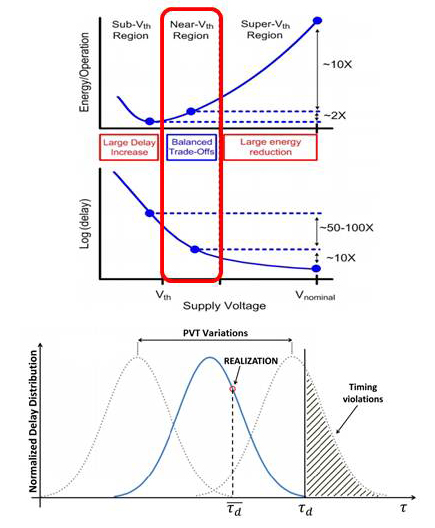

Ultra low-power computation can be achieved by combining parallel architecture with near-threshold supply voltage at advance technology node. As a matter of fact this increases the issues related to process variability and ambient temperature dependency. Standard design methodology based on design margin will lead to an energy efficiency loss.

At the IIS we are working on an ultra low-power multi-processor (PULP) shared-memory cluster realized in 28nm SOI technology. In this project, you will design HW extensions to enhance the different component (Interconnect, Core, Memory) with re-configurable knobs that can be exploited to dynamically modify the timing constrains aiming to tolerate at system level the variability effects.

By doing this project, you will gain experience in designing strategies for reliable computing system in nano-meter technology operating in near-threshold. You will learn recipes to break the design margin paradigm and enable parallel platforms to achieve maximum energy efficiency. You will also become part of the team that is currently developing the multi-processor shared-memory cluster.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Andrea Bartolini

Prerequisites

- VLSI I

- VLSI II (recommended)

Character

- 20% Theory

- 40% ASIC Design

- 40% EDA tools