Difference between revisions of "Analog"

From iis-projects

(→Available Projects) |

|||

| (17 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

| − | + | __NOTOC__ | |

| + | <!--{{DISPLAYTITLE:<span style="position: absolute; clip: rect(1px 1px 1px 1px); clip: rect(1px, 1px, 1px, 1px);">{{FULLPAGENAME}}</span>}}--> | ||

| + | = Analog and Mixed Signal Design Group = | ||

| + | The Analog and Mixed Signal Design Group is specialized in designing mixed signal integrated circuits and systems. The group divides into following research fields: | ||

| − | ==Available Projects== | + | ====[[Analog IC Design|Analog IC Design]]==== |

| + | The focus of Analog IC Design projects is on designing analog circuits, simulations and layout. The applications cover a wide range: from high-speed transceivers to power management circuits, PLL design and bio-medical front-ends to name a few. | ||

| + | |||

| + | <!-- | ||

| + | ====[[Biomedical System on Chips|Biomedical System on Chips]]==== | ||

| + | Most projects are based around our bio-medical SoC called ''VivoSoC''. It consists of specialised analogue front-ends (e.g. for ExG or neural signal acquisition, PPG based measurements, neural stimulation etc.) as well as powerful, PULP-based processor cores. Applications are in the field of optogenetics stimulation, ExG recordings (wearable and implantable), in-vivo and in-vitro experiments, neuroprosthetics etc. | ||

| + | --> | ||

| + | ====[[Wireless Communication Systems for the IoT|Wireless Communication Systems for the IoT]]==== | ||

| + | We design digital signal processing accelerators for highly integrated RF SoCs in the field of wireless communication. Our current platform with a multi-core processor system and a great RF transceiver allows us to research upcoming wireless transmission standards. One of our current focus areas is 5G cellular communication for the Internet of Things, where we offer many interesting projects for students. | ||

| + | |||

| + | =Available Projects= | ||

| + | |||

| + | ===[[Analog IC Design|Analog IC Design]]=== | ||

| + | [[File:times_adpll.png|thumb|200px|TimesADPLL: A power efficient wide loop bandwidth fractional-N all digital PLL]] | ||

<DynamicPageList> | <DynamicPageList> | ||

suppresserrors = true | suppresserrors = true | ||

category = Available | category = Available | ||

category = Analog | category = Analog | ||

| + | category = Analog IC Design | ||

</DynamicPageList> | </DynamicPageList> | ||

| − | [[ | + | ===[[Mixed Signal IC Design|Mixed Signal IC Design]]=== |

| − | |||

| − | |||

<DynamicPageList> | <DynamicPageList> | ||

suppresserrors = true | suppresserrors = true | ||

| − | category = | + | category = Available |

category = Analog | category = Analog | ||

| + | category = Mixed Signal IC Design | ||

</DynamicPageList> | </DynamicPageList> | ||

| − | + | ||

| − | === | + | <!-- |

| + | ===[[Biomedical System on Chips|Biomedical System on Chips]]=== | ||

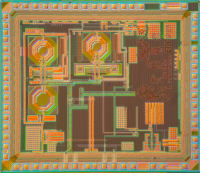

| + | [[File:vivosoc3_micrograph.png|thumb|200px|VivoSoC 3: A Multi-Sensor and Parallel Processing SoC for Miniaturised Medical Instrumentation]] | ||

| + | |||

<DynamicPageList> | <DynamicPageList> | ||

suppresserrors = true | suppresserrors = true | ||

| − | category = | + | category = Available |

category = Analog | category = Analog | ||

| − | category = | + | category = Biomedical System on Chips |

</DynamicPageList> | </DynamicPageList> | ||

| − | === | + | --> |

| + | |||

| + | ===[[Wireless Communication Systems for the IoT|Wireless Communication Systems for the IoT]]=== | ||

| + | [[File:Rfsoc_board_chip.png|thumb|200px|Our RF SoC with support for cellular communication and positioning.]] | ||

<DynamicPageList> | <DynamicPageList> | ||

suppresserrors = true | suppresserrors = true | ||

| − | category = | + | category = Available |

| − | category = | + | category = Telecommunications |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</DynamicPageList> | </DynamicPageList> | ||

Latest revision as of 18:11, 1 March 2023

Analog and Mixed Signal Design Group

The Analog and Mixed Signal Design Group is specialized in designing mixed signal integrated circuits and systems. The group divides into following research fields:

Analog IC Design

The focus of Analog IC Design projects is on designing analog circuits, simulations and layout. The applications cover a wide range: from high-speed transceivers to power management circuits, PLL design and bio-medical front-ends to name a few.

Wireless Communication Systems for the IoT

We design digital signal processing accelerators for highly integrated RF SoCs in the field of wireless communication. Our current platform with a multi-core processor system and a great RF transceiver allows us to research upcoming wireless transmission standards. One of our current focus areas is 5G cellular communication for the Internet of Things, where we offer many interesting projects for students.

Available Projects

Analog IC Design

- High-Speed Digital-to-Analog Converter (DAC) for massive MIMO testing in 65nm CMOS

- High-Speed SAR ADC for next generation wireless communication in 12nm FinFET

- Analog building blocks for mmWave manipulation

- A mmWave Voltage-Controlled-Oscillator (VCO) for beyond 5G applications

- Bluetooth Low Energy network with optimized data throughput

- 5G Cellular RF Front-end Design in 22nm CMOS Technology

- Design of Charge-Pump PLL in 22nm for 5G communication applications

Mixed Signal IC Design