Difference between revisions of "NORX - an AEAD algorithm for the CAESAR competition"

From iis-projects

(Created page with "thumb ==Short Description== Jean-Philippe Aumasson, Philipp Jovanovic, and Samuel Neves are currently developing a candidate for the [http://...") |

(→Links) |

||

| Line 66: | Line 66: | ||

==Links== | ==Links== | ||

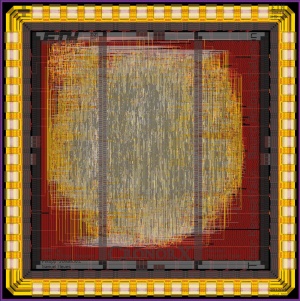

| + | * [http://asic.ethz.ch/2013/CronorX.html Chip gallery page of CronorX] | ||

| + | |||

[[#top|↑ top]] | [[#top|↑ top]] | ||

Latest revision as of 11:13, 13 June 2014

Contents

Short Description

Jean-Philippe Aumasson, Philipp Jovanovic, and Samuel Neves are currently developing a candidate for the Ceasar competion. The CAESAR competition was initialized to develop an AEAD (Authenticated Encryption with Associated Data) algorithm which combines authentication and encryption into one cryptographic entity. The resulting algorithms should be considerably faster/smaller compared to known algorithms.

The algorithm of Jovanovic et al., which is called NORX, provides up to 256 bit security. It is designed to be implemented efficiently on both hardware and software.

A detailed description of the algorithm can be found in the specification PDF.

Since there are several variations of the algorithm, it had to be decided which version(s) will be implemented.

Status: Completed

- Fall Semester 2013 (sem13h4)

- Students: Mauro Salomon, Tibor Keresztfalvi

- Supervisors: Christoph Keller, Frank K. Gürkaynak

Professor

Detailed Task Description

Goals

Practical Details

Results

During this thesis, an architecture was implemented and taped out, which supports the following features:

- Authenticated Encryption with Associated Data (AEAD)

- 128 bit or 256 bit key security

- Conigurable world width (32 and 64 bit) and nuber of F-rounds (from 2 to 16)

- Encryption and Decryption modes

- Normal and fast operation modes and scan mode for testing

- Recommended normal operation modes: NORX32-4-1, NORX32-6-1, NORX64-4-1, NORX64-6-1

Their chip Cronorx has to following properties

- Maximum throughput in normal operation mode: 2 Gbit/s

- Maximum throughput in fast operation mode (with 4 F-rounds): 10 Gbit/s

- Complexity : 59 kGE

- Clock Frequency up to 125 MHz