Difference between revisions of "File:Channel Decoding for TD-HSPA.png"

From iis-projects

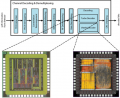

(Top: High-level architecture of the channel decoding chain for the downlink terminal side of 3GPP TD-HSPA. Bottom: Layout of the fabricated turbo and Viterbi decoder prototypes integrated in 180 nm CMOS technology.) |

(No difference)

|

Latest revision as of 10:10, 4 February 2014

Top: High-level architecture of the channel decoding chain for the downlink terminal side of 3GPP TD-HSPA. Bottom: Layout of the fabricated turbo and Viterbi decoder prototypes integrated in 180 nm CMOS technology.

File history

Click on a date/time to view the file as it appeared at that time.

| Date/Time | Thumbnail | Dimensions | User | Comment | |

|---|---|---|---|---|---|

| current | 10:10, 4 February 2014 |  | 631 × 517 (300 KB) | Kgf (talk | contribs) | Top: High-level architecture of the channel decoding chain for the downlink terminal side of 3GPP TD-HSPA. Bottom: Layout of the fabricated turbo and Viterbi decoder prototypes integrated in 180 nm CMOS technology. |

- You cannot overwrite this file.

File usage

The following page links to this file: