File list

From iis-projects

This special page shows all uploaded files.

First page |

Previous page |

Next page |

Last page |

| Date | Name | Thumbnail | Size | Description | Versions |

|---|---|---|---|---|---|

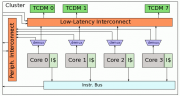

| 13:34, 16 January 2014 | Ulp cluster cimple.png (file) |  |

14 KB | 1 | |

| 15:00, 16 January 2014 | Variation Tolerant.jpg (file) |  |

132 KB | 1 | |

| 17:01, 16 January 2014 | Multiuser Equalization and Detection.jpg (file) |  |

128 KB | 1 | |

| 17:07, 16 January 2014 | Channel Estimation of 3GPP.jpg (file) |  |

142 KB | 1 | |

| 17:11, 16 January 2014 | Synchronization and Power Control Concepts.jpg (file) |  |

122 KB | 1 | |

| 17:17, 16 January 2014 | First ASIC Realization for a new HSPA.jpg (file) |  |

33 KB | 1 | |

| 17:28, 16 January 2014 | Low Silicon Area Channel Estimation for TD-SCDMA.png (file) | 46 KB | 1 | ||

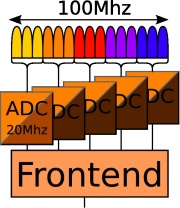

| 18:27, 16 January 2014 | Creating Bandwidth Extension with Carrier Aggregation.jpg (file) |  |

76 KB | 1 | |

| 18:41, 16 January 2014 | Creating Transmitter and Testbed Development for TD-SCDMA.jpg (file) |  |

121 KB | 1 | |

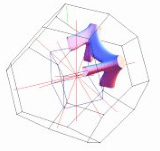

| 19:06, 16 January 2014 | Creating 3D Turbo Codes.jpg (file) |  |

40 KB | 1 | |

| 19:10, 16 January 2014 | Channel Estimation and Equalization for LTE Advanced.jpg (file) |  |

28 KB | 1 | |

| 19:13, 16 January 2014 | High-Speed DigRF-v4 Implementation.png (file) |  |

397 KB | 1 | |

| 09:36, 17 January 2014 | Reconfigurability of SHA-3 Candidates.jpg (file) |  |

9 KB | 1 | |

| 09:45, 17 January 2014 | Power Optimization in Multipliers.jpg (file) |  |

34 KB | 1 | |

| 10:41, 17 January 2014 | Low-power chip-to-chip communication network.jpg (file) |  |

21 KB | 1 | |

| 10:45, 17 January 2014 | Accelerators for object detection and tracking.jpg (file) | 26 KB | 1 | ||

| 10:58, 17 January 2014 | Zynq Zed Board.jpg (file) |  |

76 KB | 1 | |

| 11:31, 17 January 2014 | Analog Layout Engine.png (file) |  |

36 KB | 1 | |

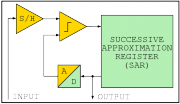

| 11:59, 17 January 2014 | Successive Approximation Register DAC.png (file) |  |

17 KB | 1 | |

| 12:05, 17 January 2014 | Assesment of novel photovoltaic architectures.jpg (file) |  |

455 KB | 1 | |

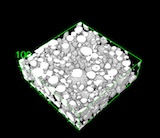

| 12:12, 17 January 2014 | Processing of 3D Micro-tomography data.jpg (file) |  |

12 KB | 1 | |

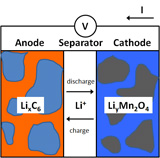

| 12:16, 17 January 2014 | Developing High Efficiency Batteries.jpg (file) |  |

34 KB | 1 | |

| 13:33, 17 January 2014 | Implementation of a 2-D model for Li-ion.jpg (file) |  |

38 KB | 1 | |

| 13:39, 17 January 2014 | Ab-initio Simulation of Strained Thermoelectric Materials.jpg (file) |  |

26 KB | 1 | |

| 15:03, 17 January 2014 | Nanotera.gif (file) |  |

6 KB | 1 | |

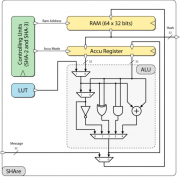

| 16:11, 28 January 2014 | Share block diagram.png (file) |  |

104 KB | Simplified block diagram of the ASIP architecture, called SHAre, supporting the SHA-2 and SHA-3 hash algorithm standards. | 1 |

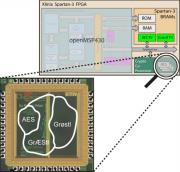

| 16:29, 28 January 2014 | Graestl.png (file) |  |

304 KB | Top: FPGA floorplan containing the microprocessor and the GrÆStl cryptographic co-processor. Bottom: Photo of the manufactured Chameleon chip, hosting a separate AES/Grøstl design and GrÆStl. | 1 |

| 17:10, 28 January 2014 | 3D board of qcrypt.png (file) |  |

278 KB | This picture shows a 3D model of the new version of the PCB. All network connections are now located on the top side of the board, making it suitable for dense housing in racks. | 1 |

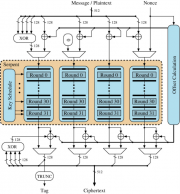

| 17:21, 28 January 2014 | Serpent high throughput.png (file) |  |

190 KB | Block diagram illustrating the OCB-Serpent architecture with four fully-unrolled Serpent cores. | 1 |

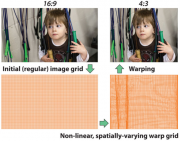

| 18:16, 28 January 2014 | Warping example.png (file) |  |

528 KB | Aspect ratio retargeting example illustrating the image domain warping steps: from an initial regular grid, we generate a spatially-varying warp grid that is used to warp the image. Original image: Courtesy of Andrew Malone (CC). | 1 |

| 18:28, 28 January 2014 | Madmax explanations.png (file) |  |

830 KB | 1 | |

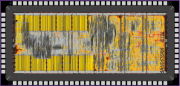

| 18:35, 28 January 2014 | Sandstorm layout.png (file) |  |

344 KB | 1 | |

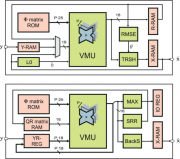

| 18:49, 28 January 2014 | AMP OMP block diagram.png (file) |  |

118 KB | 2 | |

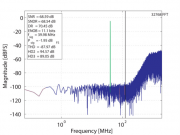

| 17:28, 29 January 2014 | Simulated spectrum of high resolution large bw.png (file) |  |

121 KB | Simulated spectrum at the output of the modulator for a sinusoidal input signal at 40MHz. | 1 |

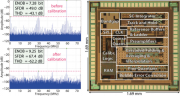

| 17:38, 29 January 2014 | Measured high resolution folding ADC.png (file) |  |

322 KB | Left: Measured output spectrum of a sinusoidal input signal at 60.123 MHz sampled at 150 MHz. Right: Chip micrograph of the implemented ADC in 130 nm CMOS. | 1 |

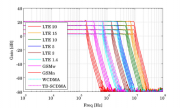

| 17:46, 29 January 2014 | Baseband filter transfer functions.png (file) |  |

194 KB | Measured baseband filter transfer functions, demonstrating the flat transfer function and the wide range of programmability in terms of frequency and gain. | 1 |

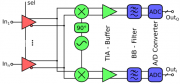

| 17:52, 29 January 2014 | Direcdt conversion receiver topology.png (file) |  |

55 KB | A direct-conversion receiver topology often used for cellular receiver, due to its good configurability. | 1 |

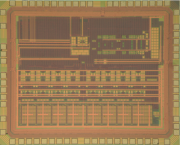

| 18:01, 29 January 2014 | Chip Micrograph of Cerebrov2.png (file) |  |

493 KB | Chip micrograph of the 8-channel sensor front-end and data acquisition IC ‘Cerebro v2’ for electrode-based medical applications, such as ECG or EEG. Implemented in a 130 nm CMOS technology. | 1 |

| 18:15, 29 January 2014 | Battery powered medical signal acquisition platform.png (file) |  |

481 KB | 1 | |

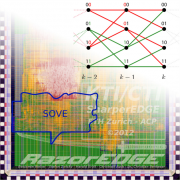

| 18:26, 29 January 2014 | Simplified trellis as used in the SOVE algorithm.png (file) |  |

617 KB | Top: Simplified trellis as used in the SOVE algorithm. Bottom: Layout of the RazorEDGE physical layer baseband ASIC. The highlighted area is occupied by the SOVE block. | 1 |

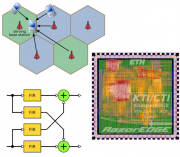

| 18:32, 29 January 2014 | Block diagram of the space-time interference canceller.png (file) |  |

302 KB | Top: Interference scenario in cellular radio. Center: Layout of the RazorEDGE baseband ASIC Bottom: Block diagram of the space-time interference canceller. | 1 |

| 17:04, 30 January 2014 | Setup of OsmoPHY together with RX board.png (file) |  |

153 KB | Top: Software architecture of the OsmoPHY framework. Bottom: Setup of OsmoPHY together with RX board, OsmocomBB and wireshark0 protocol analyzer. | 1 |

| 17:11, 30 January 2014 | High-level dedicated IR architecture storing punctured RLC blocks.png (file) |  |

135 KB | Top: Simulation results for coding schemes MCS-9 and DAS-12 in order to evalute IR performance. Bottom: High-level dedicated IR architecture storing punctured RLC blocks. | 1 |

| 17:21, 30 January 2014 | Basic working principle of the Steiner channel estimator.png (file) |  |

25 KB | Basic working principle of the Steiner channel estimator | 1 |

| 17:27, 30 January 2014 | Successive interference cancellation multi user detector.png (file) |  |

192 KB | Performance of the successive interference cancellation multi user detector (SIC-MUD) and the corresponding hardware implementation compared to the traditional linear MMSE equalizer. | 1 |

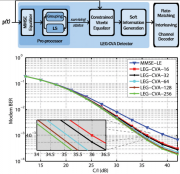

| 17:47, 30 January 2014 | Block diagram of the LEG-CVA receiver.png (file) |  |

355 KB | Top: A block diagram of the LEG-CVA receiver. Bottom: Modem Bit-Error-Rate vs. Received Signal-to-Noise Power Ratio for TD-HSPA, Case-3 Multipath Channel, 16-CDMA codes and 64-QAM. | 1 |

| 18:01, 30 January 2014 | Progressive grouping stage with MLD pruning.png (file) |  |

72 KB | A tree portion of the progressive grouping stage with MLD pruning, which is used in the pre-processing step in a low-complexity sequence detector. | 1 |

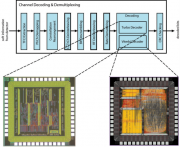

| 10:10, 4 February 2014 | Channel Decoding for TD-HSPA.png (file) |  |

300 KB | Top: High-level architecture of the channel decoding chain for the downlink terminal side of 3GPP TD-HSPA. Bottom: Layout of the fabricated turbo and Viterbi decoder prototypes integrated in 180 nm CMOS technology. | 1 |

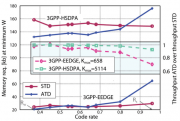

| 10:18, 4 February 2014 | Turbo Decoder Design for High Code Rates.png (file) |  |

181 KB | The impact of code rate on throughput and memory capacity of traditional acquisition-run-based turbo decoders (ATD) and state-metric-propagation-based turbo decoder implementations (STD). | 1 |

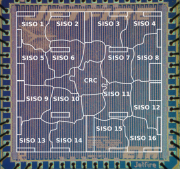

| 10:24, 4 February 2014 | High Throughput Turbo Decoder Design.png (file) |  |

804 KB | Chip micrograph of the LTE-Advanced turbo decoder. The overlay depicts the exact locations of the 16 parallel SISO decoders used to achieve the 1Gbps throughput. | 1 |

First page |

Previous page |

Next page |

Last page |