Difference between revisions of "Ultra Low-Power Oscillator"

From iis-projects

| Line 47: | Line 47: | ||

==Links== | ==Links== | ||

[[Category:Analog]] | [[Category:Analog]] | ||

| − | [[Category: | + | [[Category:Completed]] |

[[Category:Hot]] | [[Category:Hot]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

Latest revision as of 18:58, 19 December 2016

Contents

Short Description

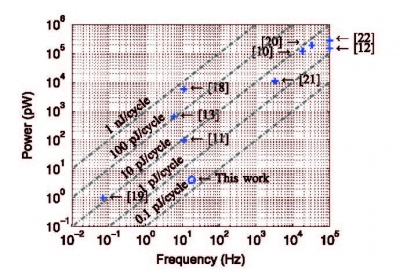

Sensor nodes for the Internet of Things must run autonomously in many cases. This means that their average power consumption must be as low as possible which is often achieved by heavy duty-cycling of operation, i.e. everything that is not needed for a particular operating state is switched off. This puts a big pressure on the power consumption of those circuits that are always on, like e.g. a system clock. So this topic has seen a lot of attention in recent years. The aim of this semester thesis is to build such an ultra low power oscillator for a frequency range up to 1 MHz based on latest research results and to achieve a comparable efficiency as the best design in the figure.

Status: Available

- Looking for 1-2 Semester students

- Contact: Thomas Burger

Prerequisites

- AIC

Character

- 20% Theory

- 80% Circuit Design