VLSI Implementation of a Low-Complexity Channel Shortener for 2G EC-GSM-IoT and Evolved EDGE

From iis-projects

Contents

Short Description

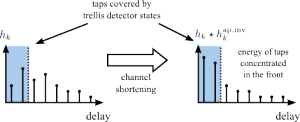

Today's wireless devices have to deal with multi-path propagation caused by reflecting objects along the receive paths. These reflections lead to a long channel impulse response, which makes the channel equalization complex. Therefore channel shortening filters are used to transform the long channel impulse response into a shorter one. At IIS during the last years, several channel shortening algorithms and implementations have been presented.

Your task in this project is to design and implement a hardware architecture of a novel channel shortening algorithm we developed recently [1]. You will get a MATLAB implementation of the algorithm as a reference implementation, from which you can start building your architecture. After you sketched a block diagram, you will implement the architecture in HDL. Synthesis and Place&Route using CAD tool lead to an ASIC implementation.

Status: In Progress

- Students: Robert Balas (sem16h28) and Georg Rutishauser (sem16h7)

- Supervision: Benjamin Weber, Matthias Korb

Character

- 30% Theory/Matlab

- 70% HDL, Synthesis, Place&Route

Prerequisites

- VLSI I

- Matlab

Professor

References

[1] Hu, Sha, et al. "A Low-complexity Channel Shortening Receiver with Diversity Support for Evolved 2G Devices." IEEE International Conference on Communications. 2016.