Difference between revisions of "Audio Video Preprocessing In Parallel Ultra Low Power Platform"

From iis-projects

| Line 27: | Line 27: | ||

[[Category:Digital]] | [[Category:Digital]] | ||

| − | |||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

Latest revision as of 10:27, 5 November 2019

Contents

Short Description

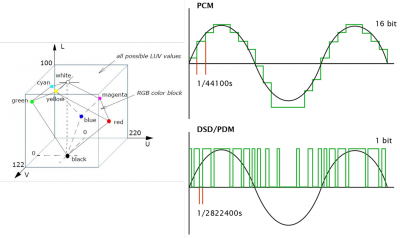

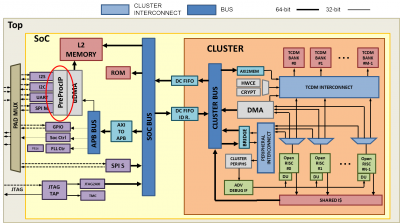

Audio and video processing on embedded systems has many constraints coming from the fewer available resources. In many cases a lot of resources are consumed during a preprocessing phase in which the raw data coming from the sensor is transformed in a proper way before being fed to the main processing algorithms. This preprocessing, in many cases,could be done very efficiently in hw reducing significantly the load on the CPU. Potential candidates include signal filtering for audio/motion sensor, sub/over sampling, color scheme conversion, image filtering, ciphering and compression/decompression. The hw IP will need to be as much as possible usable by different processing algorithms to maintain as much as possible the general purpouse phylosofy of the whole system.

The goal of this project is to evaluate the best trade off between hw and sw in the preprocessing step for few A/V processing algorithms

Status: Available

- Semester/Master Thesis

- Supervision: Antonio Pullini, Michael Schaffner

Professor

Character

- 60% Theory, Algorithms and Simulation

- 40% HW Design

Requirements

- Matlab

- Good C programming skills

- Knowledge of digital circuit design

- Knowledge of at least one HDL(VHDL, Verilog, SystemVerilog)