PULP

From iis-projects

PULP - An Open Parallel Ultra-Low-Power Processing-Platform

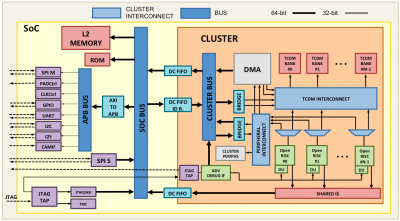

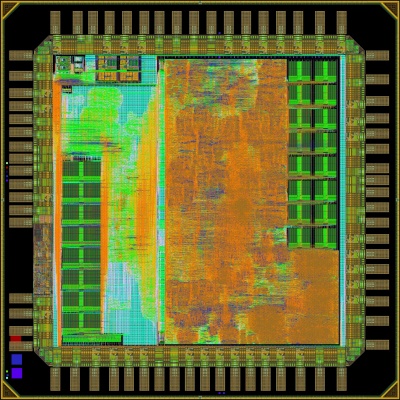

This is a joint project between the Integrated Systems Laboratory (IIS) of ETH Zurich and the Energy-efficient Embedded Systems (EEES) group of UNIBO to develop an open, scalable Hardware and Software research platform with the goal to break the pJ/op barrier within a power envelope of a few mW.

The PULP platform is a multi-core platform achieving leading-edge energy-efficiency and featuring widely-tunable performance. The aim of PULP is to satisfy the computational demands of IoT applications requiring flexible processing of data streams generated by multiple sensors, such as accelerometers, low-resolution cameras, microphone arrays, vital signs monitors. As opposed to single-core MCUs, a parallel ultra-low-power programmable architecture allows to meet the computational requirements of these applications, without exceeding the power envelope of a few mW typical of miniaturized, battery-powered systems. Moreover, OpenMP, OpenCL and OpenVX are supported on PULP, enabling agile application porting, development, performance tuning and debugging.

Inquiries from interested partners are welcome.

....more to follow.... stay tuned!

See also:

PULPino - A Small Single-Core System Based on PULP

PULPino is an open-source microcontroller like system, based on a small 32-bit RISC-V core that was developed at ETH Zurich. The core has an IPC close to 1, full support for the base integer instruction set (RV32I), compressed instructions (RV32C) and partial support for the multiplication instruction set extension (RV32M). It implements our non-standard extensions for hardware loops, post-incrementing load and store instructions, ALU and MAC operations. To allow embedded operating systems such as FreeRTOS to run, a subset of the privileged specification is supported. When the core is idle, the platform can be put into a low power mode, where only a simple event unit is active and wakes up the core in case an event/interrupt arrives.

The PULPino platform is available for RTL simulation, FPGA and the first ASIC (called Imperio) has been taped out in January 2016. It has full debug support on all targets. In addition we support extended profiling with source code annotated execution times through KCacheGrind in RTL simulations.

PULPino is based on IP blocks from the PULP project.

See also:

- Official PULP Project Website

- PULPino on GitHub

- Slides / poster from RISC-V Workshop, 2016.

- Slides from ORCONF, 2015.

Related Available Student Projects

- Structural Health Monitoring (SHM) System (1-2S/M)

- Spectrometry for Environmental Monitoring (1-2S/M)

- Waterflow Monitoring with Doppler Ultrasound (1S)

- Sound-Based Vehicle Classification and Counting (1-2S)

- Multi-Modal Environmental Sensing With GAP9 (1-2S)

- Event-based navigation on autonomous nano-drones

- A Novel Execution Scheme for Ultra-tiny CNNs Aboard Nano-UAVs

- Improved Collision Avoidance for Nano-drones

- Deep Learning-based Global Local Planner for Autonomous Nano-drones

- Training and Deploying Next-Generation Quantized Neural Networks on Microcontrollers

- Ibex: Tightly-Coupled Accelerators and ISA Extensions

- Implementation of the RISC-V Bit Manipulation (RVB) extensions for our RISC-V core

- Implementation of the RISC-V Bit Manipulation (RVB) extensions for our RI5CY core

- Scalable Heterogeneous L1 Memory Interconnect for Smart Accelerator Coupling in Ultra-Low Power Multicores

- Cerebellum: Design of a Programmable Smart-Peripheral for the Ariane Core

- Physics is looking for PULP

- Monocular Vision-based Object Following on Nano-size Robotic Blimp

- A Waypoint-based Navigation System for Nano-Size UAVs in GPS-denied Environments

- Embedded Audio Source Localization Exploiting Coincidence Detection in Asynchronous Spike Streams

- PVT Dynamic Adaptation in PULPv3

- Covariant Feature Detector on Parallel Ultra Low Power Architecture

- Ultra-High-Efficiency Power Supply Management for Ultra-Low-Power Systems on Chip

- Hardware Support for IDE in Multicore Environment

- Variability Tolerant Ultra Low Power Cluster

Related Chips

28nm

- Pulp v1 The first version of the PULP platform realized in 28nm FDSOI (RVT) technology with 4 parallel cores.

- Pulp v2 The second version of the PULP platform realized in 28nm FDSOI (LVT) technology with 4 parallel cores.

- Pulp v3 The third version of the PULP platform realized in 28nm FDSOI (RVT) technology with 4 parallel cores and a hardware accelerator.

- Honey Bunny PULp platform using RISC-V compliant RI5CY cores and Globalfoundries 28nm SLP technology. Four cores, 68 kBytes of TCDM and 256 kBytes of L2.

65nm

- Mia Wallace Third generation of PULP platform, HW accelerators, body biasing FLLs, 256 kByte memory

- Fulmine Third generation of PULP platform, Convolutional accelerator, crypto accelerator, body biasing FLLs, 256 kByte memory

- Artemis 4 core PULP system including FPU.

- Hecate 4 core PULP system with 2 shared FPUs.

- Selene 4 core PULP system with 1 shared FPU using a logarithmic number system.

- Diana 4 core PULP system with FPUs designed using approximate computing techniques.

- Phoebe an improved version of Selene, 4 cores and 1 shared vectorial FPU using logarithmic number system

- Imperio single core RISC-V based PULPino system. Has the PULP DNA, but is a single core microprocessor complete with peripherals from the PULP project.

130nm

- Vivosoc 2 core mixed-signal PULP system with a low-power A/D converter (130nm)

180nm

- Or10n An optimized implementation of the OpenRISC processor developed to be used within PULP.

- Sir10us A cryptographic application that uses the Or10n processor developed for PULP.

- Sid Large PULP chip with in-exact accelerators, LL version

- Diego Large PULP chip with in-exact accelerators, LVT version

- Manny Large PULP chip with in-exact accelerators, sub-threshold version

Publications

2016

- PULPino: A small single-core RISC-V SoC, A. Traber, F. Zaruba, S. Stucki, A. Pullini, G. Haugou, E. Flamand, F. K. Gürkaynak, L. Benini, RISC-V Workshop, 2016, slides, poster

- Enabling the Heterogeneous Accelerator Model on Ultra-Low Power Microcontroller Platforms, F. Conti, D. Palossi, A. Marongiu, D. Rossi, L. Benini, DATE, 2016 (to appear)

- High-Efficiency Logarithmic Number Unit Design based on an Improved Cotransformation Scheme, Y. Popoff, F. Scheidegger, M. Schaffner, M. Gautschi, F. K. Gürkaynak, L. Benini, DATE, 2016 (to appear)

- A 65nm CMOS 6.4-to-29.2pJ/FLOP@0.8V Shared Logarithmic Floating Point Unit for Acceleration of Nonlinear Function Kernels in a Tightly Coupled Processor Cluster, M. Gautschi, M. Schaffner, F. K. Gürkaynak, L. Benini, ISSCC, 2016, paper

2015

- A Ultra-Low-Energy Convolution Engine for Fast Brain-inspired Vision in Multicore Clusters, F. Conti, L. Benini, DATE, 2015, paper

- Lightweight virtual memory support for many-core accelerators in heterogeneous embedded SoCs, P. Vogel, A. Marongiu, L. Benini, CODES+ISSS, 2015, paper

- PULP: OpenRISC-based ultra-low power parallel platform, D. Rossi, F. Conti, A. Pullini, I. Loi, M. Gautschi, D. Palossi, A. Marongiu, G. Haugou, L. Benini, ORCONF, 2015, slidesvideo

- PULPino: A RISC-V based single-core system, A. Traber, S. Stucki, F. Zaruba, M. Gautschi, A. Pullini, I. Loi, D. Rossi, G. Haugou, F. K. Gürkaynak, L. Benini, ORCONF, 2015, slidesvideo

- Exploring Multi-banked Shared-L1 Program Cache on Ultra-Low Power Tightly Coupled Processor Clusters, I. Loi, D. Rossi, G. Haugou, M. Gautschi, L. Benini, ACM Computing Frontiers, 2015, paper

- PULP: A Ultra-Low Power Parallel Accelerator for Energy-Efficient and Flexible Embedded Vision, F. Conti, D. Rossi, A. Pullini, I. Loi, L. Benini, Journal of Signal Processing Systems, October 2015, paper

- A −1.8V to 0.9V body bias, 60 GOPS/W 4-core cluster in low-power 28nm UTBB FD-SOI technology, D. Rossi, A. Pullini, M. Gautschi, I. Loi, F.K. Gurkaynak, P. Flatresse, L. Benini, S3S, October 2015, paper

- A 60 GOPS/W, −1.8 V to 0.9 V body bias ULP cluster in 28 nm UTBB FD-SOI technology, D. Rossi, A. Pullini, I. Loi, F. K. Gürkaynak, A. Bartolini, P. Flatresse, L. Benini, Solid-State Electronics, 2016, paper

- PULP: A Parallel Ultra-Low-Power Platform for Next Generation IoT Applications, D. Rossi, F. Conti, A. Marongiu, A. Pullini, I. Loi, M. Gautschi, G. Tagliavini, A. Capotondi, P. Flatresse, L. Benini, HOT Chips, 2015, slides

- Tailoring instruction-set extensions for an ultra-low power tightly-coupled cluster of OpenRISC cores, M. Gautschi, A. Traber, A. Pullini, L. Benini, M. Scandale, A. Di Federico, M. Beretta, G. Agosta, VLSI-SoC, 2015, paper

2014

- Energy-efficient vision on the PULP platform for ultra-low power parallel computing, F. Conti, D. Rossi, A. Pullini, I. Loi, L. Benini, SiPS, 2014, paper

- Ultra-low-latency lightweight DMA for tightly coupled multi-core clusters, D. Rossi, I. Loi, G. Haugou, L. Benini, ACM Computing Frontiers, 2014, paper

- Customizing an Open Source Processor to Fit in an Ultra-Low Power Cluster with a Shared L1 Memory, M. Gautschi, D. Rossi, L. Benini, GLSVLSI, 2014, paper

- Energy efficient parallel computing on the PULP platform with support for OpenMP, D. Rossi, I. Loi, F. Conti, G. Tagliavini, A. Pullini, A. Marongiu, IEEEI, 2014, paper

Links

- Official PULP Project Website

- PULPino on GitHub

- PULP SDK (Software Development Kit)

- PULP page in University of Bologna

- LLVM compiler for PULP developed by Politecnico di Milano

Templates and Logos

This archive contains all PULP logos below as well as inverted versions thereof for dark backgrounds (in PDF and PNG formats). Also, it includes the "Orbitron" font which has been used here.

For documentation, please use the following word template word template (v1.0).