Analog Compute-in-Memory Accelerator Interface and Integration

From iis-projects

Description

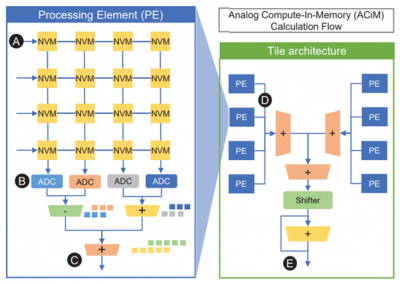

The continuous development and use of computation- and memory-intensive algorithms, such as Deep Neural Networks (DNNs) are currently being limited by the substantial energy and latency needs of off-chip memories. To tackle this issue, researchers have started investigating on structures base on non-volatile devices, that can both perform logic and arithmetic operations, and function as memories, thus starting the in-memory computing (IMC) paradigm.

One of these most novel and promising devices are the ferroelectric FETs (FeFETs), which exploit a thin ferroelectric layer between gate and channel to store data [1]. These devices can be exploited as the basic cell of analog compute-in-memory (AciM) accelerator for MAC operation that can significantly outperform the current state-of-the-art in terms of power efficiency (TOPS/W), retention time, and area scalability [2].

The target for this project is to design the interface for the ACiM accelerator and integrate the accelerator into a modern microcontroller system. In this project the student will: 1. Work in close contact with industry partners for the development of a FeFET IMC crossbar (XBAR) array 2. Design interface for ACiM accelerator 3. Integrate the accelerator with MCU 4. Verify functionality of the system

Status: In Progress

- Looking for master or semester thesis students

- Supervisor: Giorgio Cristiano, Jiawei Liao

Prerequisites

- Worked with at least one RTL language in the past (SystemVerilog or Verilog)

- Prior knowledge of hardware design and computer architecture

- VLSI I

- Knowledge of analog circuit is a plus (e.g. AIC)

Character

- 20% Literature review

- 20% Architecture Design

- 30% RTL implementation

- 30% Verification

Professor

Reference

[1] T. Soliman et al., "A Ferroelectric FET Based In-memory Architecture for Multi-Precision Neural Networks," 2020 IEEE 33rd International System-on-Chip Conference (SOCC), 2020, pp. 96-101, doi: 10.1109/SOCC49529.2020.9524750.

[2] T. Soliman et al., "Ultra-Low Power Flexible Precision FeFET Based Analog In-Memory Computing," 2020 IEEE International Electron Devices Meeting (IEDM), 2020, pp. 29.2.1-29.2.4, doi: 10.1109/IEDM13553.2020.9372124.