Successive Approximation Register (SAR) ADC

From iis-projects

Revision as of 11:59, 17 January 2014 by Kgf (talk | contribs) (Created page with "thumb|300px ==Short Description== Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to ...")

The printable version is no longer supported and may have rendering errors. Please update your browser bookmarks and please use the default browser print function instead.

Short Description

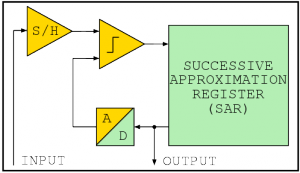

Successive Approximation Register (SAR) ADCs are the architecture of choice for medium to high resolution low-power applications, such as battery powered systems. Their architecture consists of a front-end sample-and-hold (S/H), a comparator, a decision register, and a DAC. The ADC employs a binary search algorithm to perform the conversion. This project consists of building a MATLAB model, analyzing the different circuits of the ADC, and designing and implementing a high-resolution slowly clocked SAR converter.

Status: Available

- Looking for 1-2 Semester/Master students

- Contact: Schekeb Fateh

Prerequisites

- AIC

Character

- 20% Theory

- 80% Circuit Design