A FPGA-based data streaming system that enables real-time monitoring of cell culture and neuroactivities

From iis-projects

Contents

Short Description

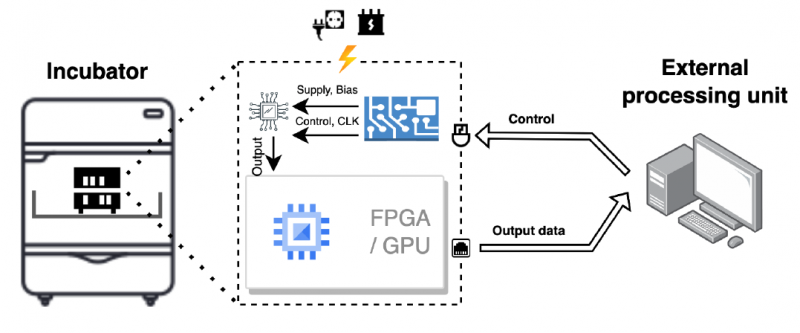

The physiology of living cells and tissues is of large interest to pharmaceutical industry for new drug development, as important information such as the drug efficacy and toxicity can be readily assessed in vitro. As such, the development of CMOS biosensors for cell monitoring and manipulation is essential. Many existing CMOS cellular sensors, however, suffer from one major limitation: of the many pixels on the sensing platform, only a handful of channels can be read concurrently, limiting our understanding of the cell culture as a whole. A newly developed platform achieves 20k concurrent channel reading, at 20kHz frame rate and 10 bit resolution. However, the vast output data stream that needs to be accessed and monitored calls for a high-speed FPGA/GPU based system with a compact, and incubator-compatible hardware design.

Status: Available

- Looking for 1 Semester/master student

- Contact: Federico Villani Hangxing Liu

Prerequisites

- Familiarity with FPGA programming (VLSI 1 or similar)

- Programming experience in Python and C++

- PCB Design (Helpful but not required)

Professor

Detailed Task Description

Possible project phases

1. Proof-of-concept FPGA system:

- - Reads data from some of the ADC outputs (even just 1 or 2) into the FPGA

- - Streams dummy data at a speed near to 10 Gbit to a storage device

- - Streams the ADC output to the PC, and visualizes a selectable subset of data

2. Hardware design:

- - Developed based on the proof-of-concept system, the hardware system reads from all ADC channels and stream the entire data to a storage device.

3. Hardware design validation:

- - The hardware design is able to stream at least some ADC outputs to the PC

4. Data compression algorithm design:

- - The FPGA implements an algorithm that leverages large on-FPGA memory to explore possibilities for data compression

Goals

- Create an highly optimized, no-frills FPGA interface capable of streaming data from 60 ASIC output channels at 160 MHz to external storage, over an ethernet interface, to ideally allow for eventual real time viewing

- Elaborate the data on-FPGA to reduce bandwidth

Practical Details