Difference between revisions of "Baseband Processor Development for 4G IoT"

From iis-projects

(Created page with "thumb|2G Testbed setup with L2/L3 processing on ZedBoard (top), double RF on evalEDGE v1.0 (middle), and baseband on ML605 (bottom). ==Short Descripti...") |

|||

| Line 1: | Line 1: | ||

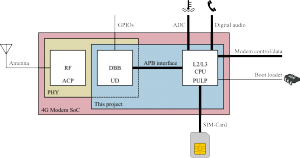

| + | [[File:4G_soc.png|thumb|4G modem SoC with RF, DBB, and L2/L3.]] | ||

[[File:2G_testbed.jpg|thumb|2G Testbed setup with L2/L3 processing on ZedBoard (top), double RF on evalEDGE v1.0 (middle), and baseband on ML605 (bottom).]] | [[File:2G_testbed.jpg|thumb|2G Testbed setup with L2/L3 processing on ZedBoard (top), double RF on evalEDGE v1.0 (middle), and baseband on ML605 (bottom).]] | ||

| Line 4: | Line 5: | ||

Various estimates predict 20 to 30 billion embedded devices connected to the Internet in 2020 in what’s called the the Internet of things (IoT). To realize this vision, cellular standards are released to meet the requirements regarding low-power and low-cost of IoT components, especially on the client side. In the latest release of the LTE standard, a new user-equipment category (Cat-0) for Machine to Machine (M2M) communications and the Internet of things (IoT) was introduced [1]. In order to develop signal processing algorithms for the fast evolving LTE landscape a fast prototyping platform is indispensable. | Various estimates predict 20 to 30 billion embedded devices connected to the Internet in 2020 in what’s called the the Internet of things (IoT). To realize this vision, cellular standards are released to meet the requirements regarding low-power and low-cost of IoT components, especially on the client side. In the latest release of the LTE standard, a new user-equipment category (Cat-0) for Machine to Machine (M2M) communications and the Internet of things (IoT) was introduced [1]. In order to develop signal processing algorithms for the fast evolving LTE landscape a fast prototyping platform is indispensable. | ||

| − | The goal of this project is to design an FPGA-based | + | A 4G cellular modem consists of an RF front-end, hardwired Digital Baseband (DBB) processing, and L2/L3 processing on a CPU. It is advantageous to use an FPGA as base. This way improvements to DBB and CPU architecture can be updated immediately to the prototype and software running on the CPU can take advantage of those improvements. |

| + | |||

| + | The goal of this project is to design an FPGA-based prototyping platform for 4G/LTE mobile communication. It shall consist of a commercial FPGA board (ML605, see [2]) and a custom RF transceiver extension card. The extension card is currently under development and will have similar features as [[evalEDGE]] but it will be LTE capable using RF solutions from [3]. The FPGA on the ML605 shall be used for RF controlling and baseband processing. In addition, the results from [[Baseband Meets CPU]] can be used to incorporate higher layer processing using a [[PULP]] CPU on the FPGA, as well. Once the testbed is running the baseband processing can be enhanced and software to run on the PULP can be written and immediately tested. | ||

===Status: Available === | ===Status: Available === | ||

: Looking for 1 Master student | : Looking for 1 Master student | ||

| − | : Supervision: [[User:Weberbe|Benjamin Weber]], [[User: | + | : Supervision: [[User:Weberbe|Benjamin Weber]], [[User:Vogelpi|Pirmin Vogel]] |

===Character=== | ===Character=== | ||

| Line 21: | Line 24: | ||

===Professor=== | ===Professor=== | ||

[http://www.iis.ee.ethz.ch/portrait/staff/huang.en.html Qiuting Huang] | [http://www.iis.ee.ethz.ch/portrait/staff/huang.en.html Qiuting Huang] | ||

| + | or | ||

| + | [http://www.iis.ee.ethz.ch/portrait/staff/lbenini.en.html Luca Benini] | ||

==References== | ==References== | ||

| Line 38: | Line 43: | ||

[[Category:Telecommunications]] | [[Category:Telecommunications]] | ||

[[Category:Weberbe]] | [[Category:Weberbe]] | ||

| − | [[Category: | + | [[Category:Vogelpi]] |

Revision as of 14:15, 28 May 2015

Contents

Short Description

Various estimates predict 20 to 30 billion embedded devices connected to the Internet in 2020 in what’s called the the Internet of things (IoT). To realize this vision, cellular standards are released to meet the requirements regarding low-power and low-cost of IoT components, especially on the client side. In the latest release of the LTE standard, a new user-equipment category (Cat-0) for Machine to Machine (M2M) communications and the Internet of things (IoT) was introduced [1]. In order to develop signal processing algorithms for the fast evolving LTE landscape a fast prototyping platform is indispensable.

A 4G cellular modem consists of an RF front-end, hardwired Digital Baseband (DBB) processing, and L2/L3 processing on a CPU. It is advantageous to use an FPGA as base. This way improvements to DBB and CPU architecture can be updated immediately to the prototype and software running on the CPU can take advantage of those improvements.

The goal of this project is to design an FPGA-based prototyping platform for 4G/LTE mobile communication. It shall consist of a commercial FPGA board (ML605, see [2]) and a custom RF transceiver extension card. The extension card is currently under development and will have similar features as evalEDGE but it will be LTE capable using RF solutions from [3]. The FPGA on the ML605 shall be used for RF controlling and baseband processing. In addition, the results from Baseband Meets CPU can be used to incorporate higher layer processing using a PULP CPU on the FPGA, as well. Once the testbed is running the baseband processing can be enhanced and software to run on the PULP can be written and immediately tested.

Status: Available

- Looking for 1 Master student

- Supervision: Benjamin Weber, Pirmin Vogel

Character

- 10% Theory

- 60% System/FPGA Design

- 30% Software

Prerequisites

- VLSI I

- Matlab, VHDL, C

Professor

References

[1] Redefining LTE for IoT. http://www.nextgcom.co.uk/wordpress/wp-content/uploads/2014/09/ARM-NextG-LTE-Cat0-White-Paper-Final.pdf, May 2015.

[2] XILINX. Virtex-6 FPGA ML605 Evaluation Kit. http://www.xilinx.com/ml605, May 2015.

[3] Advanced Circuit Pursuit, ACP AG. http://www.newacp.ch/, May 2015.