Difference between revisions of "Design of Power-Noise-Efficient Discrete-Time Amplifier Using Open-Source Tools"

From iis-projects

| Line 1: | Line 1: | ||

[[File:Kwantae Kim 2023-10-24 at 14.02.59.png|thumb|600px]][[File:Kwantae Kim 2023-10-24 at 14.04.44.png|thumb|600px]] | [[File:Kwantae Kim 2023-10-24 at 14.02.59.png|thumb|600px]][[File:Kwantae Kim 2023-10-24 at 14.04.44.png|thumb|600px]] | ||

=== Description === | === Description === | ||

| + | Energy-Efficient Circuits and Intelligent Systems (EECIS) Group recently presented an ultra-noise-efficient amplifier design using switched-capacitor circuits [1]. | ||

===Status: To be Available (On Preparation)=== | ===Status: To be Available (On Preparation)=== | ||

:Looking for master or semester thesis students | :Looking for master or semester thesis students | ||

| Line 14: | Line 15: | ||

Prof. Taekwang Jang <[mailto:tjang@ethz.ch tjang@ethz.ch]> | Prof. Taekwang Jang <[mailto:tjang@ethz.ch tjang@ethz.ch]> | ||

=== Reference=== | === Reference=== | ||

| − | [1] J. | + | [1] G. Atzeni, A. Novello, G. Cristiano, J. Liao and T. Jang, "A 0.45/0.2-NEF/PEF 12-nV/√Hz Highly Configurable Discrete-Time Low-Noise Amplifier," in IEEE Solid-State Circuits Letters, vol. 3, pp. 486-489, 2020, doi: 10.1109/LSSC.2020.3029016. |

| − | + | ||

| − | + | [2] G. Atzeni et al., "An Impedance-boosted Switched-capacitor Low-noise Amplifier Achieving 0.4 NEF," 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2022, pp. 116-117, doi: 10.1109/VLSITechnologyandCir46769.2022.9830399. | |

| + | |||

| + | [3] G. Atzeni, C. Livanelioglu, L. Recchioni, S. Arjmandpour and T. Jang, "An Energy-Efficient Impedance-Boosted Discrete-Time Amplifier Achieving 0.34 Noise Efficiency Factor and 389 MΩ Input Impedance," 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185212. | ||

| + | |||

[[#top|↑ top]] | [[#top|↑ top]] | ||

[[Category:EECIS]] | [[Category:EECIS]] | ||

Revision as of 14:09, 24 October 2023

Contents

Description

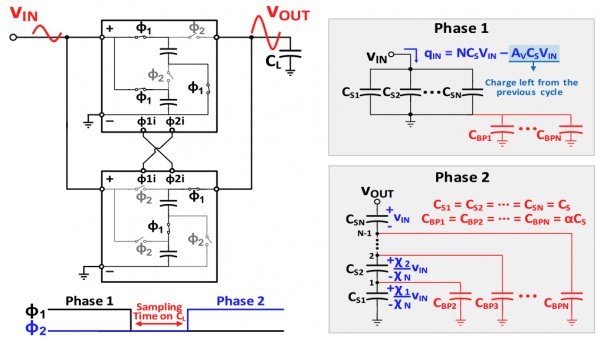

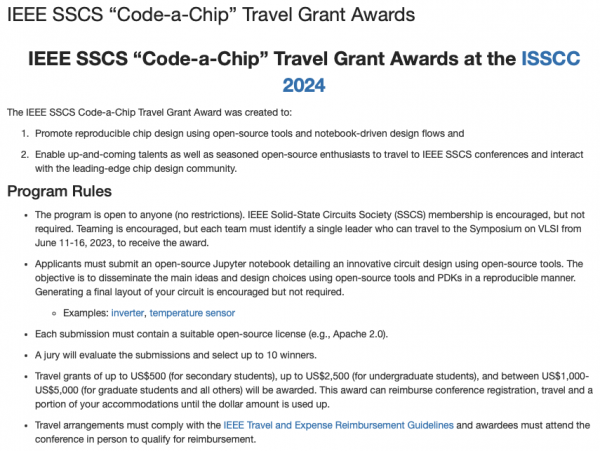

Energy-Efficient Circuits and Intelligent Systems (EECIS) Group recently presented an ultra-noise-efficient amplifier design using switched-capacitor circuits [1].

Status: To be Available (On Preparation)

- Looking for master or semester thesis students

- Supervisor: Kwantae Kim

Prerequisites

- Python

- Analog Integrated Circuits

Character

- 20% Literature review

- 20% Theory

- 60% Programming

Professor

Prof. Taekwang Jang <tjang@ethz.ch>

Reference

[1] G. Atzeni, A. Novello, G. Cristiano, J. Liao and T. Jang, "A 0.45/0.2-NEF/PEF 12-nV/√Hz Highly Configurable Discrete-Time Low-Noise Amplifier," in IEEE Solid-State Circuits Letters, vol. 3, pp. 486-489, 2020, doi: 10.1109/LSSC.2020.3029016.

[2] G. Atzeni et al., "An Impedance-boosted Switched-capacitor Low-noise Amplifier Achieving 0.4 NEF," 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2022, pp. 116-117, doi: 10.1109/VLSITechnologyandCir46769.2022.9830399.

[3] G. Atzeni, C. Livanelioglu, L. Recchioni, S. Arjmandpour and T. Jang, "An Energy-Efficient Impedance-Boosted Discrete-Time Amplifier Achieving 0.34 Noise Efficiency Factor and 389 MΩ Input Impedance," 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185212.