Difference between revisions of "Design of a Fused Multiply Add Floating Point Unit"

From iis-projects

| Line 44: | Line 44: | ||

| − | [[Category:Digital]] [[Category:Semester Thesis | + | [[Category:Digital]] [[Category:Semester Thesis]] [[Category:UlpSoC]] [[Category:2016]] [[Category:ASIC]] [[Category:PULP]] |

Latest revision as of 10:26, 5 November 2019

Contents

Short Description

Floating point units (FPU) are one part of a micro-processor and usually directly integrated in the pipeline. In a multi-processor environment one private FPU per processor core is not the most energy efficient implementation because floating point (FP)-operations are not always used which means they remain idle for lots of cycles. Sharing FPUs among the processors is expected to improve the utilization of the FPUs and therefore reduce the overall power consumption of the system. We have already designed a FPU unit with support for FP-additions, FP-subtractions, and FP-Multiplications and shared in a multi-core cluster PULP. Since it is a simple architecture, it consumes only little area and gives only little area savings when it is shared in a cluster.

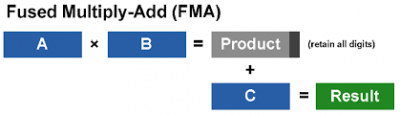

In linear algebra we often face multiply-add operations which could be very efficiently handled by an FPU which is capable of doing multiply-add in a fused unit.

Your task will be to come up with an hardware efficient architecture for a fused multiply-add FPU, implement it in System Verilog and plug it to the RISC-V processor.

Status: Available

- Supervisors: Michael Gautschi, Michael Schaffner

Prerequisites

- VLSI I

- Interest in Computer Architectures

- System Verilog knowledge

Character

- 25% Theory

- 50% ASIC Design

- 25% Verification