Difference between revisions of "FPGA-based Implementation of a Novel Cell-Search Algorithm for Mobile Communications"

From iis-projects

(Created page with "thumb|300px ==Short Description== Current and future mobile communication networks rely on the cellular topology. The ability of a mobile user equ...") |

|||

| Line 56: | Line 56: | ||

[[Category:Hot]] | [[Category:Hot]] | ||

[[Category:Digital]] | [[Category:Digital]] | ||

| + | [[Category:FPGA]] | ||

| + | [[Category:Telecommunications]] | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

Revision as of 16:32, 3 February 2015

Contents

Short Description

Current and future mobile communication networks rely on the cellular topology. The ability of a mobile user equipment (UE) such as a mobile phone to search for nearby cell towers and select the best available one to establish a connection is very crucial. At IIS, we have invented a new technique for the cell-search functionality in 3rd/4th generation mobile communication systems, which provides superior performance to known techniques. During the cell-search process, the mobile UE has to synchronize the local oscillator frequency relative to the carrier. Otherwise, the signal integrity is highly compromised and the overall performance is severely degraded.

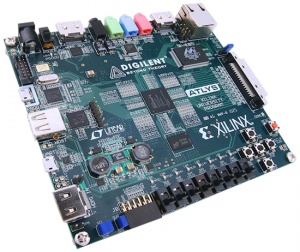

To this end, the student will study and port the Matlab implementation of the algorithm to VHDL in order to implement the new technique on a powerful state-of-the-art FPGA board. After testing and verifying the hardware implementation, the VHDL code will be integrated with the rest of the already-implemented chip solution; thereby completing the whole baseband receiver chain.

Status: Available

- Suitable for a Semester project or a Master thesis

- Contact: Karim Badawi

Prerequisites

- Knowledge of the VLSI1 Lecture

- Interest in Mobile Communications

- Knowledge of Matlab (or willingness to learn)

- VHDL knowledge would be advantageous but not necessary

Character

- 10% Theory

- 15% Matlab

- 60% VHDL / FPGA Implementation

- 15% Testing & Results