Glitches Reduce Listening Time of Your iPod

From iis-projects

Contents

Short Description

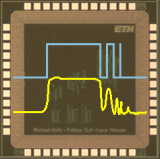

Even though glitching in digital circuits and the resulting extra power dissipated by glitches (also called glitching power) has been addressed in the literature for many years, it hasn't found its way into EDA. Current synthesis tools are not able to report nor optimize glitching. As a result glitching power goes mainly unnoticed in today's ASICs. On the other hand, glitching power can be a significant part of total power dissipated on a chip. Therefore, reporting and optimization of glitching power signifies a very promising and overdue addition to EDA tools. As a prerequisite, it is important to have an assessment of how much glitching power contribution exists in typical ASICs and how effective existing glitch-reduction techniques are for its reduction. The goal of this project is to simulate glitching power contributions in ASIC circuits and to investigate various glitch reduction techniques for their efficency in reducing glitching power and suitability for incorporation into an automatic synthesis environment. An ASIC designed with sample circuits containing different anti-glitch methods shall also allow measurements and comparisons with simulations.

Status: Completed

- Pascal Hertrich

- Supervision: Hubert Kaeslin

Prerequisites

- VLSI I

- VLSI II (recommended)

Character

- 30% ASIC design

- 20% Theory

- 50% EDA tools