Difference between revisions of "Implementing Hibernation on the ARM Cortex M0"

From iis-projects

(Implement hibernation for the ARM Cortex M0) |

|||

| Line 36: | Line 36: | ||

[[#top|? top]] | [[#top|? top]] | ||

[[Category:Digital]] | [[Category:Digital]] | ||

| + | [[Category:Hot]] | ||

| + | [[Category:System Design]] | ||

[[Category:Available]] | [[Category:Available]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

[[Category:Phager]] | [[Category:Phager]] | ||

Revision as of 14:21, 2 September 2015

Contents

Short Description

In Internet of Thing (IoT) applications, energy is often available only sporadically. Since power can be lost at any time, processing larger tasks on a microcontroller in this environment requires special measurements to be taken in order to avoid restarting the entire task after each power outage.

Check-pointing, i.e., saving the processor state at predefined stages during processing, is a way to resume computation after a power outage. If a warning signal is available before the power outage, i.e., the supply voltage is dropping, the processor state can be saved only when a power outage is imminent and thus superfluous saving operations are avoided.

Both scenarios require a mechanism to save a snapshot of the processor state in a non-volatile memory. This mechanism is commonly known as hibernation.

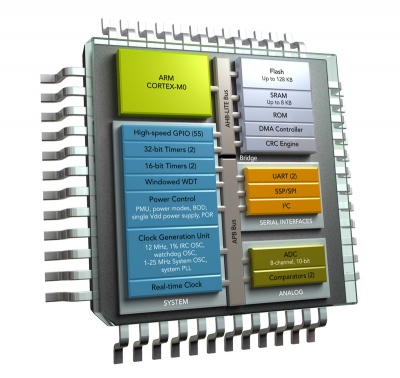

The goal of this Semester Thesis/Group Project is to implement a proper hibernation mechanism for the ARM Cortex M0. The basic procedure for the hibernation mechanism will be provided, but will have to be adapted. In a first step, the student will have to get a deep understanding of the processor architecture. In a second step, he will implement the hibernation mechanism in C and Assembler. In a last step, the student will perform measurements to evaluate the transitions cost to enter and leave the hibernation mode.

If time permits, the project can be extended to a heterogeneous dual-core ARM Cortex M4/M0, or alternatively, different hibernation mechanism and strategies can be implemented and evaluated.

Status: Available

- Semester Thesis/Group Project

- Supervision: Pascal Alexander Hager (IIS)

Professor

Character

- 50% Theory

- 30% Implementation

- 20% Measurements

Requirements

- Basic Knowledge of C

- Understanding of general processor architectures and concepts (TIK lectures)