Difference between revisions of "Resource Partitioning of RPC DRAM"

From iis-projects

(Created page with "<!-- Resource Partitioning of RPC DRAM (1-2S/B) --> Category:Digital Category:Computer Architecture Category:SW/HW Predictability and Security Category:HW/SW Sa...") |

|||

| Line 28: | Line 28: | ||

= Introduction = | = Introduction = | ||

| + | |||

Recently, a new class of off-chip memories hit the market, targeting low area and low pin-count FPGAs and ASICs. These reduced pin count DDR (RPC DDR) [1] memories only require a simple on-chip PHY and can operate with regular digital IO pads making them usable on our ASICs. | Recently, a new class of off-chip memories hit the market, targeting low area and low pin-count FPGAs and ASICs. These reduced pin count DDR (RPC DDR) [1] memories only require a simple on-chip PHY and can operate with regular digital IO pads making them usable on our ASICs. | ||

In previous projects, we implemented a memory-controller for RPC DRAM and taped it out on two different chips [2][3]. | In previous projects, we implemented a memory-controller for RPC DRAM and taped it out on two different chips [2][3]. | ||

| + | |||

| + | [[File:Rpc_dram.png|thumb|350px|]] | ||

= Project = | = Project = | ||

Revision as of 11:18, 15 November 2022

Contents

Overview

Status: Available

- Type: Bachelor or Semester Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

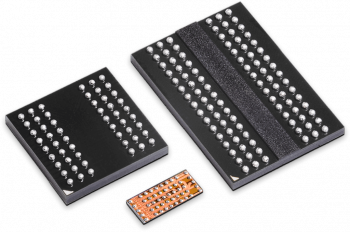

Recently, a new class of off-chip memories hit the market, targeting low area and low pin-count FPGAs and ASICs. These reduced pin count DDR (RPC DDR) [1] memories only require a simple on-chip PHY and can operate with regular digital IO pads making them usable on our ASICs.

In previous projects, we implemented a memory-controller for RPC DRAM and taped it out on two different chips [2][3].

Project

The goal of the project is to investigate and implement resource partitioning schemes [4] in the memory-controller to improve predicatability of memory accesses. The memory controller is part of a larger platform hosting a linux capable RISC-V 64-bit core.

- Get familiar with RPC DRAM protocol and the controller design

- Study existing resource partitioning techniques

- Implement and verify on FPGA

- Benchmark results

Character

- 20% Literature Review

- 60% Hardware Design

- 20% Verification and Bechmarking

Prerequisites

- Strong interest in computer architecture and memory systems

- Experience with digital design in SystemVerilog as taught in VLSI I

- Preferred: Knowledge or experience with AXI and RISC-V

References

[1] “Etron Technology Inc. RPC DRAM.” https://etronamerica.com/products/rpc-dram/

[4] “Supporting Temporal and Spatial Isolation in a Hypervisor for ARM Multicore Platforms” https://retis.sssup.it/~a.biondi/papers/isol-ICIT18.pdf