Resource Partitioning of RPC DRAM

From iis-projects

Contents

Overview

Status: Available

- Type: Bachelor or Semester Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

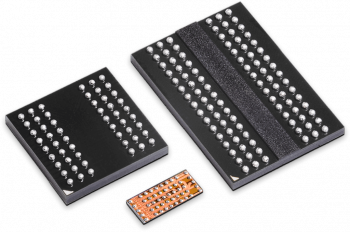

Recently, a new class of off-chip memories hit the market, targeting low area and low pin-count FPGAs and ASICs. These reduced pin count DDR (RPC DDR) [1] memories only require a simple on-chip PHY and can operate with regular digital IO pads making them usable on our ASICs.

In previous projects, we implemented a memory-controller for RPC DRAM and taped it out on two different chips [2][3].

Project

The goal of the project is to investigate and implement resource partitioning schemes [4] in the memory-controller to improve predicatability of memory accesses. For example, Arm Memory System Resource Partitioning and Monitoring (MPAM)[5] is a recent example of such a scheme. The memory controller is part of a larger platform hosting a linux capable RISC-V 64-bit core.

- Get familiar with RPC DRAM protocol and the controller design

- Study existing resource partitioning techniques

- Implement and verify on FPGA

- Benchmark results

Character

- 20% Literature Review

- 60% Hardware Design

- 20% Verification and Bechmarking

Prerequisites

- Strong interest in computer architecture and memory systems

- Experience with digital design in SystemVerilog as taught in VLSI I

- Preferred: Knowledge or experience with AXI and RISC-V