Difference between revisions of "Low-power Temperature-insensitive Timer"

From iis-projects

(Created page with "thumb|300pxthumb|300px === Description === The rapid growth of the internet of things leads to high demand for the cont...") |

(→Reference) |

||

| Line 27: | Line 27: | ||

=== Reference=== | === Reference=== | ||

[1] T. Jang, M. Choi, S. Jeong, S. Bang, D. Sylvester, and D. Blaauw, “5.8 A 4.7nW 13.8ppm/°C self-biased wakeup timer using a switched-resistor scheme,” in 2016 IEEE International Solid-State Circuits Conference (ISSCC), Jan. 2016, pp. 102–103. doi: 10.1109/ISSCC.2016.7417927. | [1] T. Jang, M. Choi, S. Jeong, S. Bang, D. Sylvester, and D. Blaauw, “5.8 A 4.7nW 13.8ppm/°C self-biased wakeup timer using a switched-resistor scheme,” in 2016 IEEE International Solid-State Circuits Conference (ISSCC), Jan. 2016, pp. 102–103. doi: 10.1109/ISSCC.2016.7417927. | ||

| + | |||

[2] G. Cristiano, J. Liao, A. Novello, G. Atzeni, and T. Jang, “A 8.7ppm/°C, 694nW, One-Point Calibrated RC Oscillator using a Nonlinearity-Aware Dual Phase-Locked Loop and DSM-Controlled Frequency-Locked Loops,” in 2020 IEEE Symposium on VLSI Circuits, Jun. 2020, pp. 1–2. doi: 10.1109/VLSICircuits18222.2020.9162838. | [2] G. Cristiano, J. Liao, A. Novello, G. Atzeni, and T. Jang, “A 8.7ppm/°C, 694nW, One-Point Calibrated RC Oscillator using a Nonlinearity-Aware Dual Phase-Locked Loop and DSM-Controlled Frequency-Locked Loops,” in 2020 IEEE Symposium on VLSI Circuits, Jun. 2020, pp. 1–2. doi: 10.1109/VLSICircuits18222.2020.9162838. | ||

| + | |||

[3] M. Ding, M. Song, E. Tiurin, S. Traferro, Y.-H. Liu, and C. Bachmann, “A 0.9pJ/cycle 8ppm/oC DFLL-based Wakeup timer Enabled by a Time-Domain Trimming and An Embedded Temperature Sensing,” p. 2. | [3] M. Ding, M. Song, E. Tiurin, S. Traferro, Y.-H. Liu, and C. Bachmann, “A 0.9pJ/cycle 8ppm/oC DFLL-based Wakeup timer Enabled by a Time-Domain Trimming and An Embedded Temperature Sensing,” p. 2. | ||

Revision as of 15:45, 7 June 2021

Description

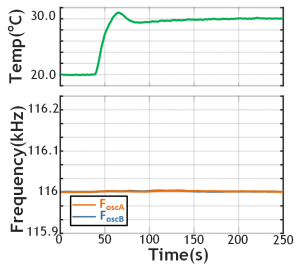

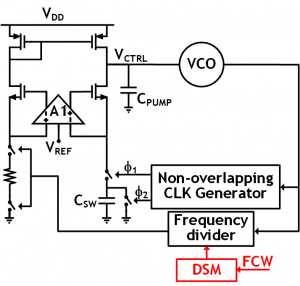

The rapid growth of the internet of things leads to high demand for the continuous monitoring of environmental and biomedical signals. To satisfy the requirement for duty-cycled wireless IoT devices, the timer needs to be precise and low-power. Conventional crystal-based timer is bulky. RC-based timer is a good alternative that can be integrated on-chip [1][2][3]. Capacitors are relatively insensitive to temperature change, so it is critical to control the resistors to achieve temperature-stable timer.

In this project, the student will: 1. Study prior art 2. Characterizing on-chip resistors 3. Exploring and developing novel on-chip timer

Status: Available

- Looking for master or semester thesis students

- Supervisor: Jiawei Liao,Giorgio Cristiano

Prerequisites

- AIC

- VLSI

Character

- 20% Literature review

- 20% Theory

- 30% Device characterization

- 30% Design and simulation

Professor

Prof. Taekwang Jang <tjang@ethz.ch>

Reference

[1] T. Jang, M. Choi, S. Jeong, S. Bang, D. Sylvester, and D. Blaauw, “5.8 A 4.7nW 13.8ppm/°C self-biased wakeup timer using a switched-resistor scheme,” in 2016 IEEE International Solid-State Circuits Conference (ISSCC), Jan. 2016, pp. 102–103. doi: 10.1109/ISSCC.2016.7417927.

[2] G. Cristiano, J. Liao, A. Novello, G. Atzeni, and T. Jang, “A 8.7ppm/°C, 694nW, One-Point Calibrated RC Oscillator using a Nonlinearity-Aware Dual Phase-Locked Loop and DSM-Controlled Frequency-Locked Loops,” in 2020 IEEE Symposium on VLSI Circuits, Jun. 2020, pp. 1–2. doi: 10.1109/VLSICircuits18222.2020.9162838.

[3] M. Ding, M. Song, E. Tiurin, S. Traferro, Y.-H. Liu, and C. Bachmann, “A 0.9pJ/cycle 8ppm/oC DFLL-based Wakeup timer Enabled by a Time-Domain Trimming and An Embedded Temperature Sensing,” p. 2.